# KHR SNO S<sup>®</sup>

# SYCL State of the Union Keynote SYCLcon 2022 Specification Release

#### **Michael Wong**

SYCL Codeplay Distinguished ISOCPP Foundation ISO C++ Direction michael@codeplay.com | wongmichael.co

This work is licensed under a Creative Commons Attribution 4.0 International License

# **Programming Models Must Persist**

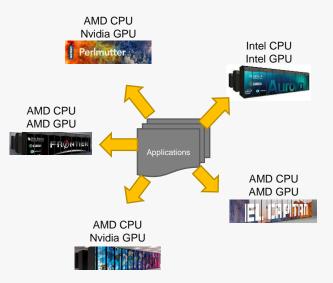

#### US National Laboratory Supercomputers 2021-2023

- HPC and now exascale computing requires programming models that endure for future workloads, > 20 years

- But Hardware changes frequently, constant improvement

- Programming models, have to be stable but also support latest HW,

Requires an open interface, across architectures with multiple implementations

# SYCL 2020 Launched February 2021

### Expressiveness and simplicity for heterogeneous programming in modern C++

Closer alignment and integration with ISO C++ to simplify porting of standard C++ applications Improved programmability, smaller code size, faster performance Based on C++17, backwards compatible with SYCL 1.2.1 **Backend acceleration API independent**

### **New Features**

Unified Shared Memory | Parallel Reductions | Subgroup Operations | Class template Argument Deduction

This work is licensed under a Creative Commons Attribution 4.0 International License

2

т

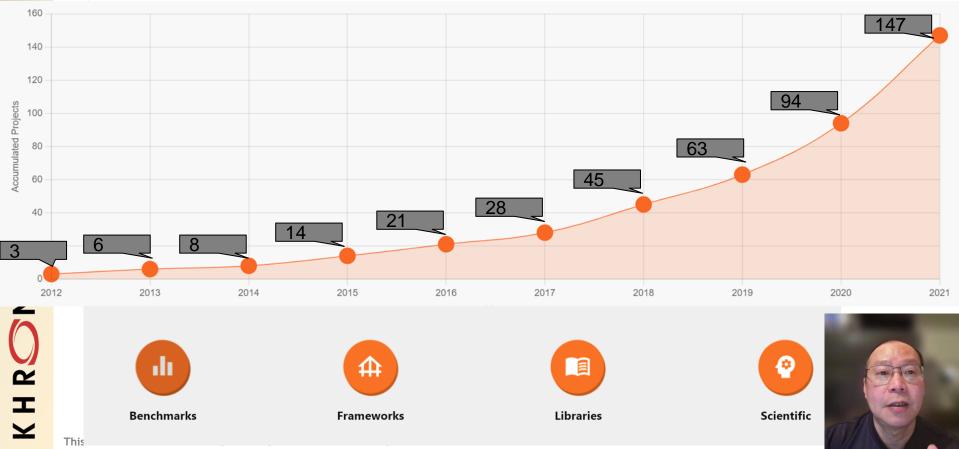

# SYCL Projects cumulative growth

#### Projects - SYCL.tech

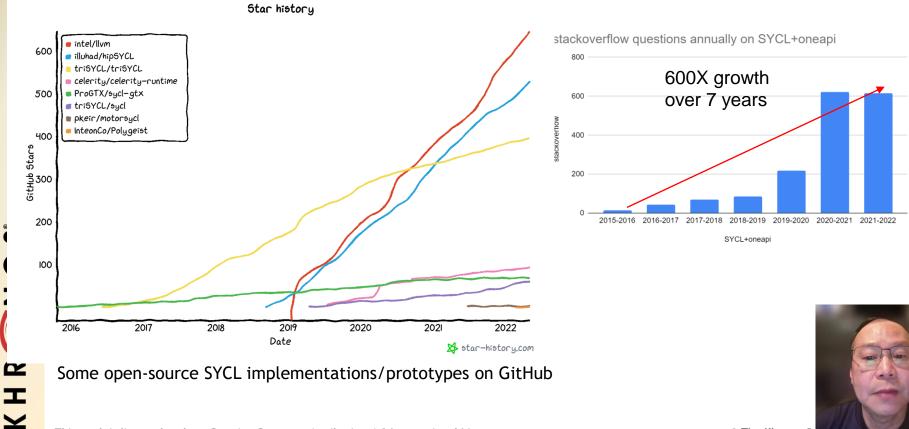

# SYCL user and developer Phenomenal Growth

This work is licensed under a Creative Commons Attribution 4.0 International License

# Github SYCL source files is over 30000

| Repositori        | 0 21,44                                                                                                                                                                                                 | 21,446 code results |                                   |                                                                                                                       |                     | <cl sycl.hpp=""> in Jan, 2022<br/>21 K in April, 2022</cl> |                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------|-----------------------------------------------------------------------------|

| Code<br>Commits   |                                                                                                                                                                                                         | 12                  |                                   | eneous-computing-we<br>ent/unit2/oneapi.ı                                                                             |                     |                                                            |                                                                             |

| Issues            | 5                                                                                                                                                                                                       | 3                   | 18 {{< e<br>19<br>20 <b>**E</b> ) | mbed-pdf url="pdf/:<br>"#include <sycl sycl.hp<="" td=""><td></td><td></td><td>Issues Marketplace Explore</td></sycl> |                     |                                                            | Issues Marketplace Explore                                                  |

| Packages          |                                                                                                                                                                                                         | 0                   | 21<br>22 <b>*Ex</b> a<br>23       | Re                                                                                                                    | positories          |                                                            | 8,804 code results                                                          |

| Marketpla         | ce                                                                                                                                                                                                      | 0                   | 23<br>24 <b>```(</b><br>25 #ind   | Co                                                                                                                    | ode<br>ommits       | 1K<br>277                                                  | xfong/sycl                                                                  |

| Topics            |                                                                                                                                                                                                         | 0                   | 26 cons<br>27 usir                |                                                                                                                       | ues                 | 152                                                        | library/include/sycl_engine.hpp 1 #ifndef RUNTING SUBJECT 2 2 #define RUNTI |

| 8.2k mentions of  | #include <syc< td=""><td>L/sycl.hpp&gt; in Ja</td><td>an, 2022</td><td></td><td>scussions<br/>ckages</td><td>3</td><td>3 #include <cl <br="">4 namespace syc<br/>5<br/>6 #endif // RUM</cl></td></syc<> | L/sycl.hpp> in Ja   | an, 2022                          |                                                                                                                       | scussions<br>ckages | 3                                                          | 3 #include <cl <br="">4 namespace syc<br/>5<br/>6 #endif // RUM</cl>        |

| 8.8 K in Apr, 202 | 2                                                                                                                                                                                                       |                     |                                   | Ма                                                                                                                    | arketplace          |                                                            | 7<br>8 #include "crc                                                        |

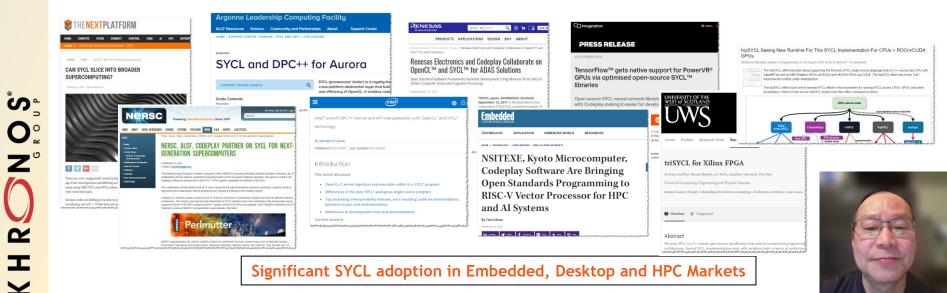

### Market needs SYCL: easy to build SYCL on any device

| 2016 | 19-21 April, 2016<br>Vienna, Austria | 2022 | IWOCL and SYCLcon 2022<br>10 <sup>th</sup> International Workshops<br>on OpenCL and SYCL |

|------|--------------------------------------|------|------------------------------------------------------------------------------------------|

| -    | 21 projects                          | -    | 147 projects                                                                             |

| -    | 2 implementations in work            | -    | >12 implementations in work                                                              |

| -    | 3-4 platforms                        | -    | 10+ platforms                                                                            |

| -    | SYCL was a TSG of OpenCL             | -    | SYCL is independent WG of Khronos                                                        |

| -    | 10 members attending TSG             | -    | 20+ members attending WG                                                                 |

| -    | <10 GitHub stars                     | -    | >600 GitHub stars                                                                        |

| -    | <10 StackOverflow questions          | -    | >600 StackOverflow questions                                                             |

| -    | No Safety Critical                   | -    | Safety Critical Exploratory Group                                                        |

| -    | No book, a few articles              | -    | 1 book, many articles                                                                    |

| -    | < 100 GitHub include code            | _    | ~30000 GitHub include code                                                               |

| -    | No Supercomputing presence           | -    | SC BoF 5 years in a role                                                                 |

| -    | No automotive                        | _    | Renesas R-Car                                                                            |

| -    | No Clang/LLVM                        | _    | Clang/LLVM DPC++ activ                                                                   |

| -    | No common one-stop website           | _    | SYCL.tech                                                                                |

| -    | No common teaching material          | _    | SYCL Academy                                                                             |

| -    | No HPC                               | -    | ~7 HPC systems                                                                           |

This work is licensed under a Creative Commons Attribution 4.0 International License

°S O N N N

HR

$\mathbf{\Sigma}$

# SYCL is mainstream

- Open Standards and Open Source implementations

- Open cross-company collaboration

- Co-design for all forms of extreme heterogeneity

- SYCL Survey coming

Q\* What language functionality would you like to see more broadly supported?

- C++20 as the core language

- C++23 as the core language

- Unified Shared Memory (USM)

- Unnamed kernel lambda functions

- Hierarchical Parallelism improvements

- ] None

- Other (Comment)

This work is licensed under a Creative Commons Attribution 4.0 International License

K H R N N O S

# Market needs SYCL to Evolve (call to action)

2022

- More workloads, NAMD, GROMACS, ROOTS

- Compile more ISO C++ as C++ advances •

- CTS, SDK, Compiler explorer

- SYCL Graphs •

- SPEC Accel/HPC Benchmarks

- Wikipedia, FAQ

- Safety Critical

- Educational videos

- Public CTS nodes •

- More ecosystem, more libraries •

- SYCL MLIR

ັ້

O° ≝

Z°

2

Т

$\mathbf{\Sigma}$

- Public CTS does •

- SYCL interpreter, Jupyter notebook •

- More Vendor adoption •

- Better tooling, profilers, debuggers, analyzers •

- Data movement is still King, Will get worse with sparsity •

- CUDA to SYCL conversion

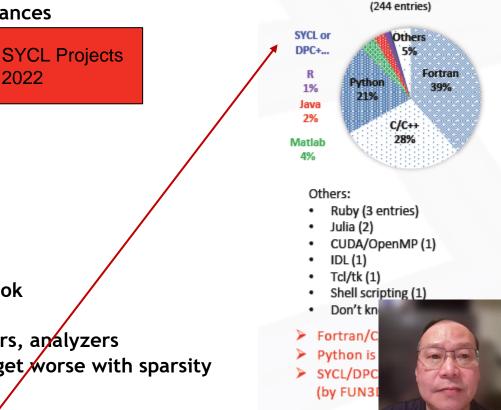

- Parallelism Survey 2022 at NASA This work is licensed under a Creative Commons Attribution 4 Olators

International License

© The Khronos®

Programming Languages

# Market needs SYCL to succeed in democratizing

Q\* Which of these provisional and vendor extensions would you like to see become Khronos extensions?

- Scoped Parallelism: <u>View via hipSYCL</u>

- Multi-device queue: <u>View via hipSYCL</u>

- Command group properties: <u>View via hipSYCL</u>

- Buffer-USM interop: <u>View via hipSYCL</u>

- Pipes: View via Intel

- Accessor restrict property: View via Intel

- Accessor properties: View via Intel

- Enqueue barrier: <u>View via Intel</u>

- Bfloat16: View via Intel

- Properties: View via Intel

- ] None

ຶ້

O°₂ Z°

2

Т

This work is licensed under a Creative Commons Attribution 4.0 International License

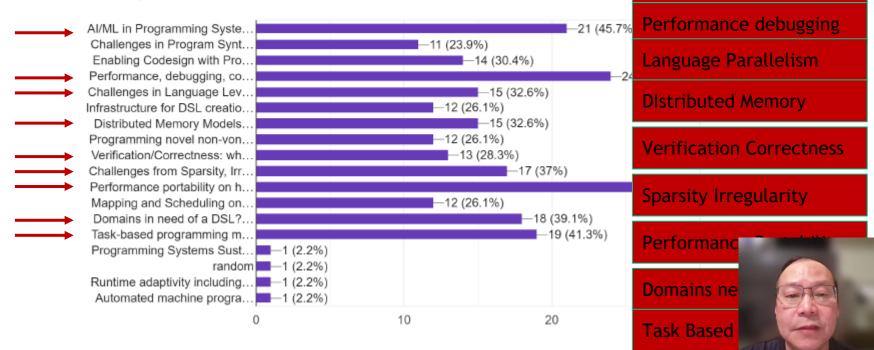

### From the recent Programming Systems Research Forum at DOE Feb 2022

Please rate your interest in participating in each of these potential breakout group topics. Pick at

most six (6) topics. We are saving two breakout grou...I free to suggest a topic in the Compilers with AI/ML

This work is licensed under a Creative Commons Attribution 4.0 International License

## From ASCR Workshop Mar 2021

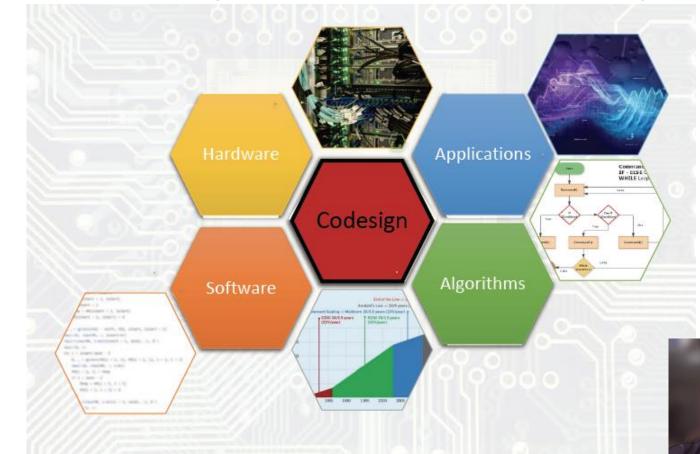

#### ASCR Workshop on Reimagining Codesign

https://www.orau.gov/ASCR-CoDesign/

This work is licensed under a Creative Commons Attribution 4.0 International License

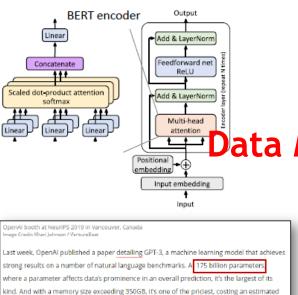

# From Flops to TOPS in ML

°S O 2 V V

2 2

т

$\mathbf{\Sigma}$

This work is licensed under a creative common ger building of the mational License Just-hype-dark-ai-silicon-disguises ht

### From Torsten Hoefler talk: Stop counting and start moving (data) Data movement is all you need

% flop

99.80

% Runtime

61.0

DATA MOVEMENT IS ALL YOU NEED: A CASE STUDY ON OPTIMIZING TRANSFORMERS

#### Andrei Ivanov \*1 Nikoli Dryden \*1 Tal Ben-Nun 1 Shigang Li 1 Torsten Hoefler

#### ABSTRACT

Transformers are one of the most important machine learning workloads today. Training one is a very computeintensive task, often taking days or weeks, and significant attention has been given to optimizing transformers. Despite this, existing implementations do not efficiently utilize GPUs. We find that data movement is the key bottleneck when training. Due to Amdahl's Law and massive improvements in compute performance, training has now become memory-bound. Further, existing frameworks use suboptimal data layouts. Using these insights, we present a recipe for globally optimizing data movement in transformers. We reduce data movement by up to 22.91% and overall achieve a 1.30× performance improvement over state-of-the-art frameworks when training a BERT encoder layer and 1.19× for the entire BERT. Our approach is applicable more broadly to optimizing deep neural networks, and offers insight into how to tackle emerging performance bottlenecks.

#### 1 INTRODUCTION

Transformers (Vaswani et al., 2017) are a class of deep neural network architecture for sequence transduction (Graves, 2012), with similar applicability as RNNs (Rumelhart et al., 1986) and LSTMs (Hochreiter & Schmidhuber, 1997). They have recently had a major impact on natural language processing (NLP), including language modeling (Radford et al., 2018; Wang et al., 2018; 2019), question-answering (RaMicrosoft, 2020b), number of training samples (Raffel et al., 2019; Liu et al., 2019), and total iterations (Liu et al., 2019; dominant task for machine learning compute where training even cause environmental concerns (Strubell et These trends will only accelerate with pushes tow

Kaplan et al., 2020). These all significantly increase compute requirements. Indeed, transformers are becoming the a model can cost tens of thousands to millions of dewith tens of billions to trillions of parameters (N

#### Statistical normalization 0.17 25.5 Element-wise 0.03 13.5 Data Movement°is still King

highly

optimized

#### Our performance improvement for BERT-large

30% over PyTorch

Operator class

Tensor contraction

- 20% over Tensorflow + XLA

- 8% over DeepSpeed

est. savings on AWS over PyTorch: \$85k for BERT. \$3.6M GPT-3

#### This work is licensed under a Creative Commons Attribution 4.0 International License

Even Deep Learning will be limited by data movement (arXiv:2007.00072)

Sparsity in Deep Learning: Pruning and growth for efficient inference and training in neural networks

TORSTEN HOEFLER, ETH Zürich, Switzerland

- DAN ALISTARH, IST Austria, Austria

- TAL BEN-NUN, ETH Zürich, Switzerland

- NIKOLI DRYDEN, ETH Zürich, Switzerland

- ALEXANDRA PESTE, IST Austria, Austria

The growing energy and performance costs of deep learning have drive of neural networks by selectively pruning components. Similarly to th networks generalize just as well, if not better than, the original dense memory footprint of regular networks to fit mobile devices, as well as sho networks. In this paper, we survey prior work on sparsity in deep learning of sparsification for both inference and training. We describe approach neural networks, different training strategies to achieve model sparsity, ar practice. Our work distills ideas from more than 300 research papers and who wish to utilize sparsity today, as well as to researchers whose goal include the necessary background on mathematical methods in sparsi as early structure adaptation, the intricate relations between sparsity a techniques for achieving acceleration on real hardware. We also define a m that could serve as a baseline for comparison of different sparse network 54 sparsity can improve future workloads and outline major open problema

The supreme goal of all theory is to make the irreducible basic of possible without having to surrender the adequate representation of

\$12 million to train.

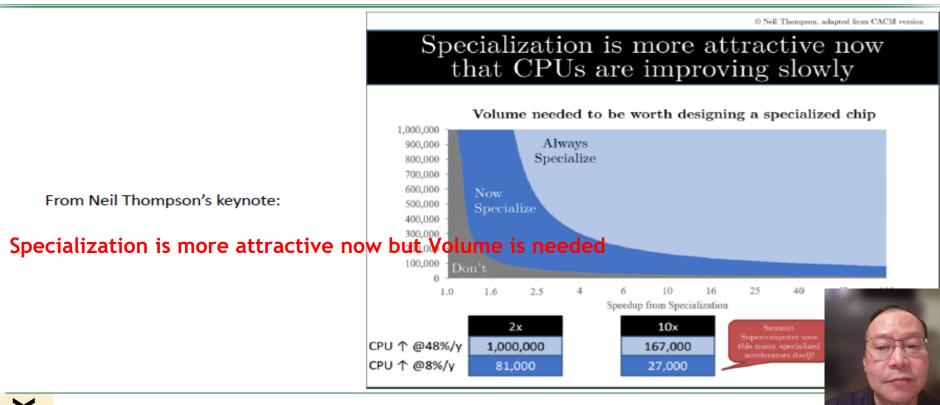

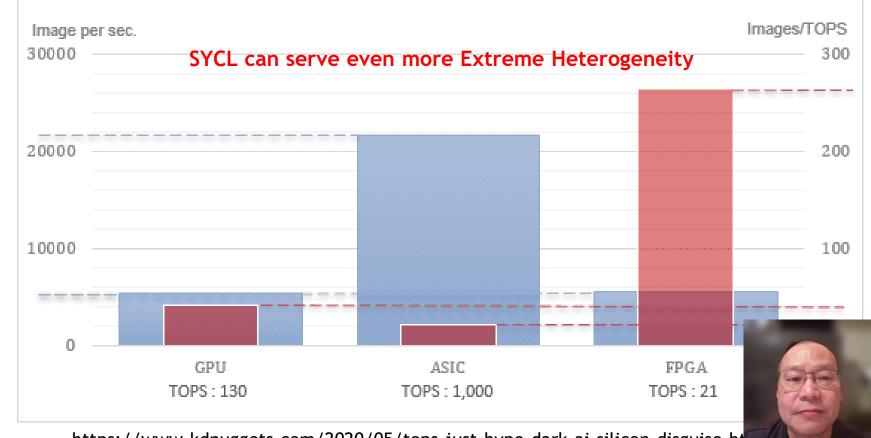

### We need Codesign with extreme Heterogeneity

This work is licensed under a Creative Commons Attribution 4.0 International License https://doi.org/10.2172/1822498 os® G

### Future SYCL: Emerging transformative technologies

Т

$\mathbf{\Sigma}$

- Chiplets and Superchips

- Licensable IP for Server-class processors (ARM)

- Open Source Hardware and Open Silicon Compilers (RISC-V)

- Photonic Resource Disaggregation (Ayar Labs TeraPhy, ARPA-E ENLITENED, and DARPA PIPES)

- Standardized Accelerator Interfaces (CCIX, Coherent PCIe, CXL, UCIe, HSA, Intel Level-0 & DSA)

- Advanced Hardware description Languages and Hardware generator

- New Accelerators (Ex: AMD/Xilinx Versal, SambaNova, Graphcore, Cerebras...)

- Advanced Packaging Technologies for Heterogeneous

Integration (HIR) https://eps.ieee.org/technology/heterogeneous-integration roadmap/2019-edition.html

- Open Source and Extensible Compiler Framewor MLIR)

- Al integrated applications

- Programming Abstractionses Frameworks, and J

# **Parallel Industry Initiatives**

OpenCL

OpenCL 1.2

**OpenCL C Kernel**

Language

2011

SYCL 1.2 C++11 Single source programming

OpenCL 2.1 SPIR-V in Core

2015

IR

SYCL 1.2.1 C++11 Single source programming

OpenCL 2.2

SPIR

2017

SYCL 2020 C++17 Single source programming Many backend options

OpenCL 3.0

2020

C++23

SYCL 202X C++20 Single source programming Many backend options

This work is licensed under a Creative Commons Attribution 4.0 International License

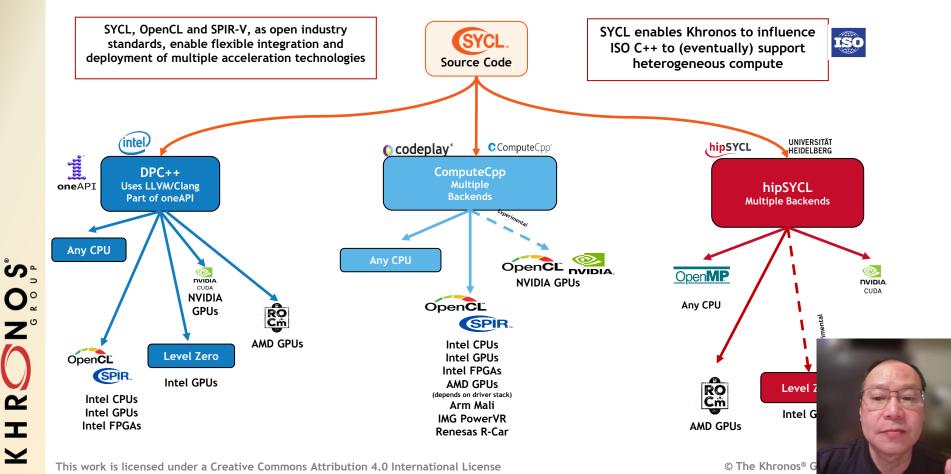

### SYCL Implementations in Development (2022/05/01)

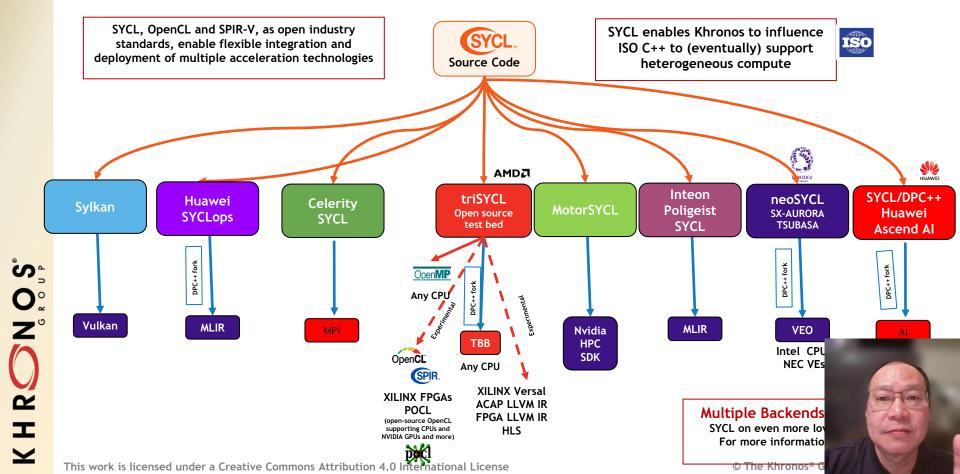

### SYCL Experimental Development (2022/05/01)

# Migration advice by Platform (2022/05/05): For a device kind, which SYCL compiler?

ALTERA

|        |     | .&habana' |       | Eirebr |

|--------|-----|-----------|-------|--------|

| Google | gro | Q.        | GRAPH | CORE   |

@

ועח

Y Tenstorrent

SambaNova

XILINX

- NVIDIA GPUs

- DPC++ supported today by Codeplay, open-source, optimized

- AMD GPUs

- hipSYCL open-source today is better and is supporting European Processor initiative in LUMI & Karolina

- DPC++ experimental support today by Codeplay, open-source

- Intel GPUs

- DPC++ supported by Intel

- New hardware:

- Codeplay supports a range of new hardware with ComputeAorta + ComputeCpp, including RISC-V custom hardware and GPU IP from Imagination Technologies and ARM, as well as Renesas R-Car for automotive

- Also can do it on their own (DIY)

- FPGA

- DPC++ compiler for Intel FPGAs

- AMD/Xilinx has triSYCL prototype for FPGA & CGRA

- AI/ML/NN

- All the major implementations/companies can customize support or you can build it DIY

- RISC-V

- Codeplay has developed ACORAN stack for RISC-V as an accelerator

- CPU

- All major SYCL implementations

This work is licensed under a Creative Commons Attribution 4.0 International License

### SYCL Ecosystem, Research and Benchmarks 2022/05/01

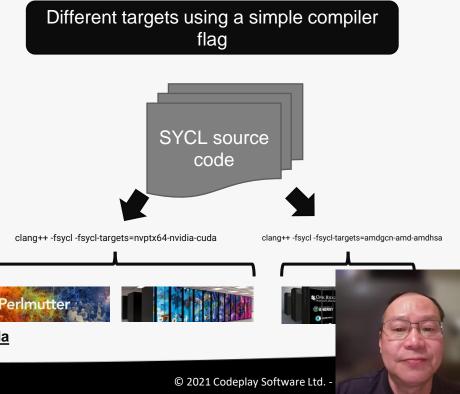

# Nvidia and AMD Support in DPC++

22

- Extending DPC++ to target Nvidia and AMD GPUs

- Supporting Perlmutter, Polaris and Frontier supercomputers

- Open source and available to everyone

- Codeplay commercially supports these implementations

https://www.codeplay.com/oneapiforcuda Resources for AMD coming soon

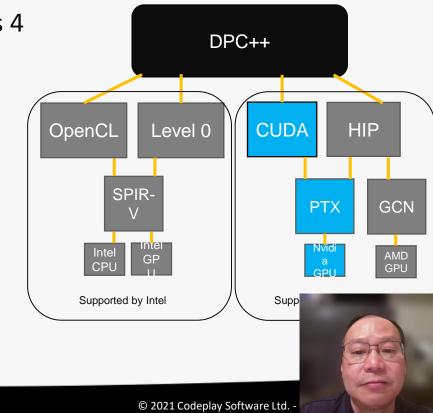

# CUDA as a backend

- The DPC++ runtime currently implements 4 SYCL backends:

- OpenCL

- Level Zero

- CUDA

- HIP

- Moving up a level of abstraction, you untether your codebase from specific hardware

- Developers have flexibility to prioritize performance

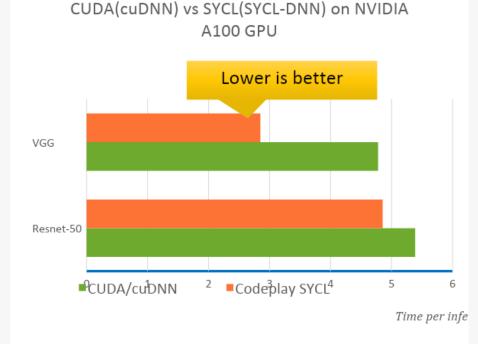

# Performance comparison

- SYCL uses the same C++ performance model as CUDA, so it achieves very similar performance for the same code

- SYCL makes it easy to write parameterizable code that adapts the algorithms to underlying hardware: this enables automatic optimizations that increase performance

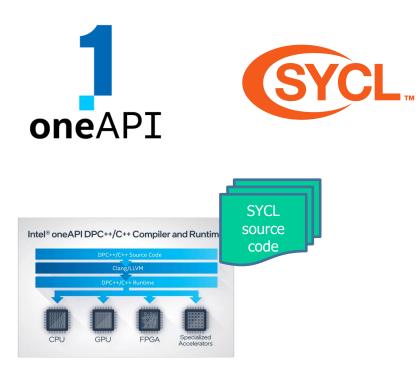

# oneAPI and SYCL

- SYCL sits at the heart of oneAPI

- Provides an open standard interface for developers

- Defined by the industry

# **SYCL Enables Supercomputers**

National Energy Research Scientific Computing Center

This work is licensed under a Creative Commons Attribution 4.0 International License

# Towards a Portable Pipeline in Drug Discovery

- The LIGATE project aims at building a portable drug discovery pipeline

- Funded from the European High-Performance Computing Joint Undertaking Joint Undertaking (JU)

- HPC is heading toward specialization and extreme heterogeneity

- SYCL enables to write platform independent code, while keeping nativecomparable performance

# SYCL as a universal programming model for HPC

Starting with US National Labs

\*\*

This work is license\_

MELUXINA

Across Europe, Asia are many Petascale and pre-exascale systems

• With many variety of CPUs GPUs FPGAs, custom devices

CZECH REPUBLI

MareNostrum 4

© The Khronos® (

• Often with interconnected usage agreements

\_ive Commons Attribution 4.0 International License

Europe EPI: hipSYCL in Loonardo, Lumi and Karolina

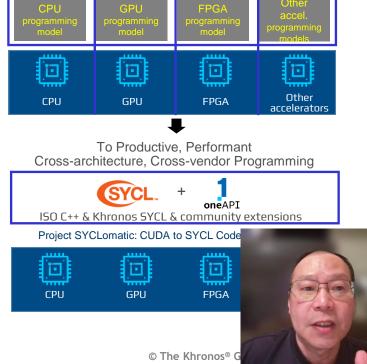

### Easier, Short Path to Heterogeneous Programming

Coming Soon: An Open Source CUDA<sup>\*</sup> to SYCL<sup>\*</sup> Code Migration Tool - Project SYCLomatic, DPCT

### SYCL\* with oneAPI open, cross-architecture, standardsbased programming

Allows developers to expand the value of their investments across architectures

Provides choice in hardware & freedom from proprietary, single-vendor lock-in

#### Intel is providing a CUDA<sup>\*</sup> to SYCL<sup>\*</sup> migration tool: Project SYCLomatic

Enables developers a productive path to create single-source, portable code

for hardware targets regardless of vendor

Simplifies development while delivering performance, reduces time & costs for code maintenance

A community to share, collaborate & contribute software technologies

#### Available on GitHub by end of May

github.com/oneapi-src/SYCLomatic github.com/oneapi-src/SYCLomatic-test

Use the tool, please provide feedback!

### Simplify Heterogeneous Development

From Diverse Programming Approaches

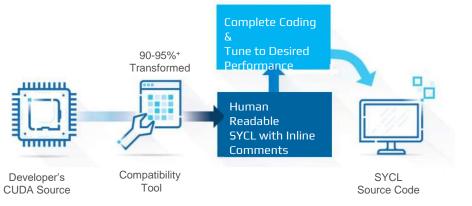

### SYCLomatic Tool Usage Workflow (newly open sourced by the end of May)

Collect compilation options of the Developer's CUDA<sup>\*</sup> source from project build scripts, eg. Makefile, vcxproj file

<u>Assist</u> developers migrating code written in CUDA to SYCL by generating SYCL code wherever possible

Typically, 90%-95%<sup>+</sup> of CUDA code automatically migrates to SYCL code

Inline comments are provided to help developer complete and tune the code

Other names and brands may be claimed as the property of others.

This work is licensed under a Creative Commons Attribution 4.0 International License

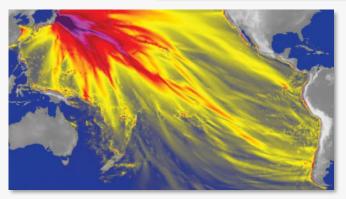

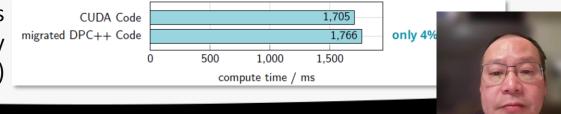

### Case Study: Zuse Institute Berlin

From CUDA to DPC++ and back to Nvidia GPUs... and FPGAs

A oneAPI case study with the tsunami simulation easyWave

Even on NVIDIA GPU, SYCL code is only 4% slower (with Codeplay developed open-source compiler)

- Originally written for NVIDIA GPUs with CUDA

- Auto-converted to SYCL (DPC++) with Intel's Compatibility Tool

- Resulting SYCL code runs on: NVIDIA GPU, Intel GPU, Intel CPU, Intel FPGA [ + any new processor with SYCL support ]

**()** codeplay\*

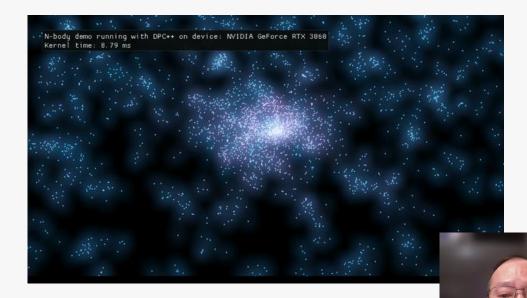

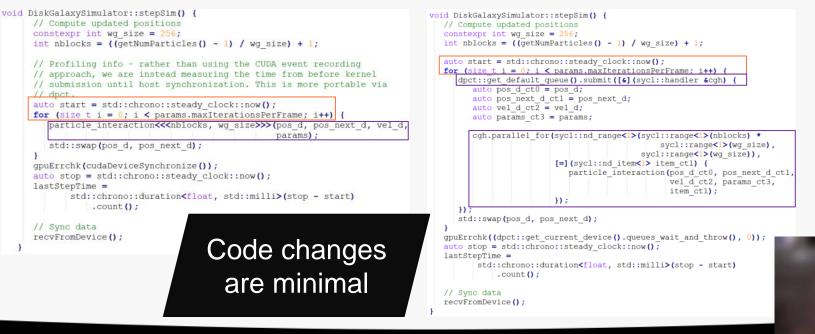

# N-Body

• Simulates gravitational interaction in a fictional galaxy

$$\vec{F_i} = -\sum_{i \neq j} G \frac{(\vec{r_i} - \vec{r_j})}{|\vec{r_i} - \vec{r_j}|^3}$$

https://github.com/topics/n-bodysimulator

# Familiar Standard C++ Code

### CUDA

codeplay\*

### SYCL

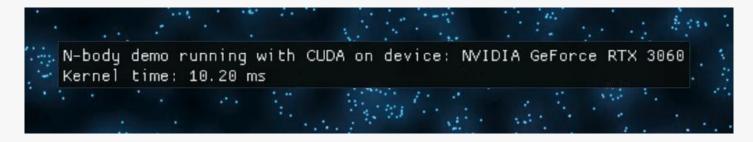

# **Performance Achieved**

N-body demo running with DPC++ on device: NVIDIA GeForce RTX 3060 Kernel time: 8.79 ms

www.codeplay.com/oneapiforcuda/

# JOIN SYCL Safety-Critical Exploratory Forum Now

open and royalty-free high-level compute APIs suitable for safety-critical markets Proven Khronos More information and **Exploratory Process to** signup instructions ensure industry Khronos SYCL Safety-Critical requirements are fully https://www.khronos.org/syclsc **Exploratory Forum** understood before starting standardization initiatives Any company is welcome to join Online discussion forum and weekly Zoom calls Initiation of No cost or IP Scope of Khronos Working Work Licensing obligations No detailed design activity Group to execute Document Project NDA to cover the SOW to protect participants IP **Exploratory Forum** Discussions Agreed SOW Explore if consensus can be built around an document released agreed Scope of Work document from NDA and made public Discuss what standardization activities can best execute actions in the Scope of Work

S O N N N

HR

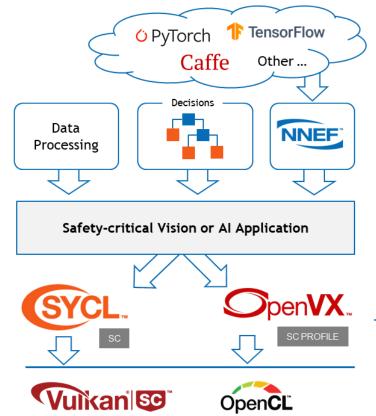

# SYCL SC in the Khronos SC Ecosystem

S O Z V

2

ΗX

Neural network models are trained in the cloud using a variety of platforms.

Once the model is trained it is exported and converted to NNEF before being passed to a safety-critical API for inferencing.

**OpenVX** provides high level APIs for Vision and AI with a safety-critical profile, enabling applications to quickly deploy trained NN models.

SYCL SC provides a general parallel programming API for accelerated compute at the C++ level. A typical AI application pipeline will combine the discreet functionality exposed by OpenVX with proprietary algorithms written using SYCL SC involving data pre-processing and post-processing, as well as complex decision making.

Vulkan SC or OpenCL are lower, execution-level APIs that cou used to accelerate higher-level APIs like SYCL SC & OpenVX

This work is licensed under a Creative Commons Attribution 4.0 International License

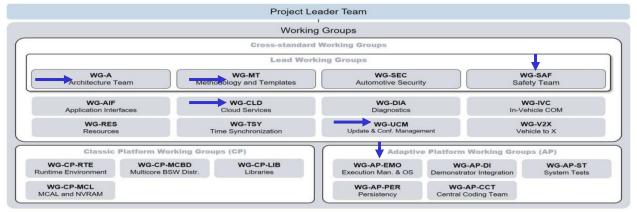

# Khronos AUTOSAR Liaison What next?

#### CROSS-STANDARD LEAD WORKING GROUPS (FO, CP, AP)

AUT@SAR Design guidelines for using parallel processing technologies on Adaptive Platform **3D Graphics** AUTOSAR AP R19-11 Desktop, Mobile **Document Title** Design guidelines for using and Web parallel processing technologies on Adaptive Platform AUTOSAR Document Owner AUTOSAR **Document Responsibility** WebGL **Document Identification No** 884 **Document Status** published Part of AUTOSAR Standard Adaptive Platform Part of Standard Release R19-11

This work is licensed under a Creative Commons Attribution 4.0 International License

### Case Study: Automotive Al

- Codeplay provides a full open-standards software stack (SYCL/OpenCL/SPIR-V) for the Renesas R-Car AI system-on-chip

- This enables easy transition from NVIDIA GPU platforms to R-Car platform

"For Renesas, SYCL is a key enabler for automotive ADAS/AD software developers that allows them to easily use the highly-efficient, heterogeneous accelerators of the R-Car SoC Series through the open Khronos standard,"

# Final words

- Programming Models Must Persist

- SYCL 2020 Launched February 2021

- SYCL user and developer Phenomenal Growth

- Market needs SYCL: easy to build SYCL on any device

- SYCL is mainstream

- Market needs SYCL to Evolve (call to action)

- SYCL can serve even more Extreme Heterogeneity

- Data Movement is still King

- We need Codesign with extreme Heterogeneity

- Future SYCL: Emerging transformative technologies

- SYCL can be a part of a standard programming model for all HPC ,Embedded AI/ML, and Automotive

- SYCL is an open standard with multiple company contributions, lots European/Asia projects

# **Enabling Industry Engagement**

- SYCL working group values industry feedback

- https://community.khronos.org/c/sycl

- https://sycl.tech

- SYCL Academy

- https://github.com/codeplaysoftware/syclacademy

- SYCL FAO

- https://www.khronos.org/blog/sycl-2020-what-do-you-need-to-know

- SYCL Survey coming **Advisory Panel**

Chaired by Tom

Deakin of U of Bristol

**Regular meetings to**

give feedback on

specifications

roadmap and draft

#### Public contributions to Specification, Conformance Tests and software

https://github.com/KhronosGroup/SYCL-CTS https://github.com/KhronosGroup/SYCL-Docs https://github.com/KhronosGroup/SYCL-Shared https://github.com/KhronosGroup/SYCL-Registry https://github.com/KhronosGroup/SvclParallelSTL

> Invited Experts https://www.khronos.org/advisors/

Khronos members https://www.khronos.org/members/

https://www.khronos.org/registry/SYCL/

Khronos SYCL Forums, Slack Channels, Stackoverflow, reddit, and SYCL.tech Khronos GitHub

Contribute to SYCL open source specs, CTS, tools and ecosystem

SYCL Advisory SYCL Panels Working Group

https://community.khronos.org/c/svcl/ https://stackoverflow.com/guestions/tagged/sycl

Open to all!

https://www.reddit.com/r/sycl https://github.com/codeplaysoftware/syclacademy https://sycl.tech/

https://community.khronos.org/www.khr.io/slack https://app.slack.com/client/TDMDFS87M/CE9UX4CHG

This work is licensed under a Creative Commons Attribution 4.0 International License