# **OpenCL Compiler Tools for FPGAs**

Dmitry Denisenko, Engineering Programmable Solutions Group, Intel April 21, 2016

#### **Motivation**

- Great performance comes from deep understanding of hardware <u>architecture</u>, <u>compiler</u>, and the <u>algorithm</u>.

- Compiler tools must educate the user about the underlying architecture and how user's algorithm fits onto it.

# How differences in FPGA architecture lead to differences in OpenCL FPGA compiler tools.

### **Talk Overview**

# How are FPGAs different from other architectures?

- 1. Computation in Space versus Time

- 2. Importance of Area

- 3. Loop Pipelining

- 4. Local Memory Flexibility

- 5. (other ways we're not going to cover here)

# Altera SDK for OpenCL Tools that deal with these concepts.

# **1. Computation in Space**

now part of Intel

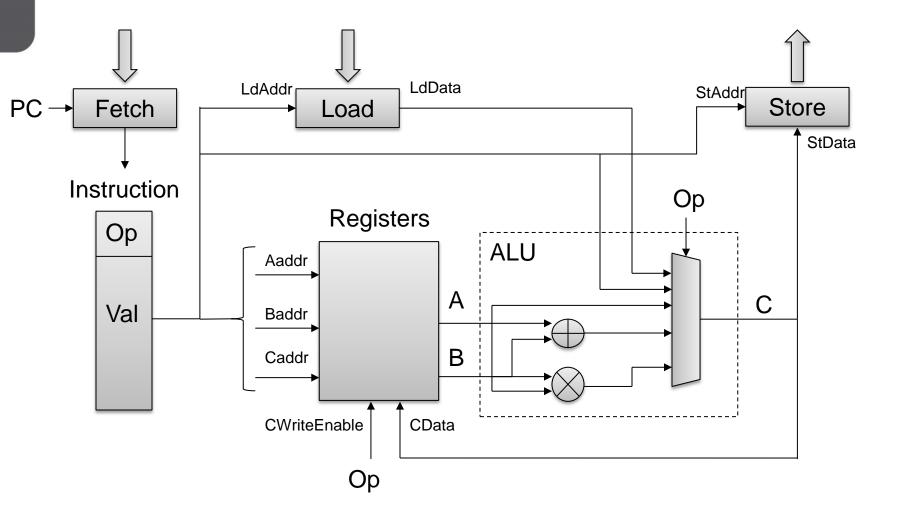

# A simple 3-address CPU

# Load memory value into register

# Add two registers, store result in register

# A simple program

Mem[100] += 42 \* Mem[101]

CPU instructions:

R0  $\leftarrow$  Load Mem[100] R1  $\leftarrow$  Load Mem[101] R2  $\leftarrow$  Load #42 R2  $\leftarrow$  Mul R1, R2 R0  $\leftarrow$  Add R2, R0 Store R0  $\rightarrow$  Mem[100]

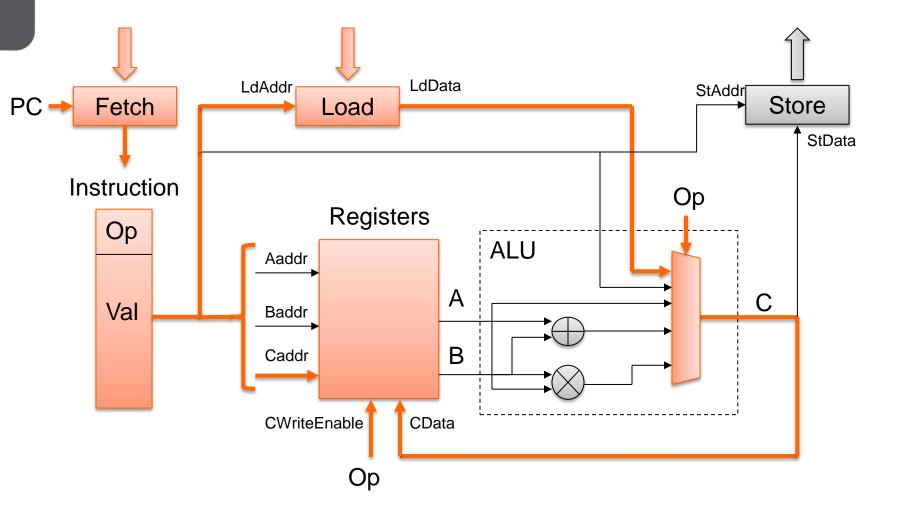

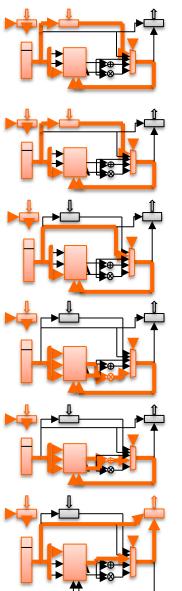

# CPU activity, step by step

R0 ← Load Mem[100]

R1 ← Load Mem[101]

R2 ← Load #42

R2 ← Mul R1, R2

R0 ← Add R2, R0

Store R0  $\rightarrow$  Mem[100]

# Time

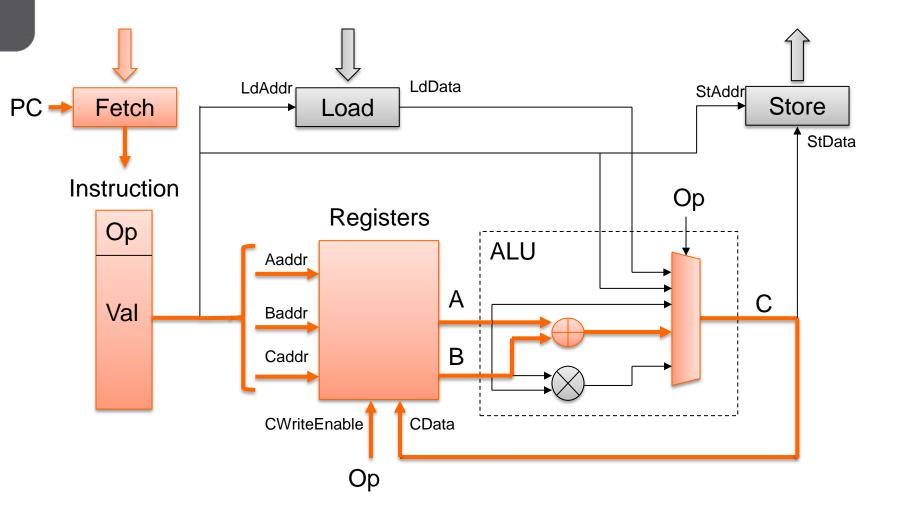

# Unroll the CPU hardware...

R0 ← Load Mem[100]

R1 ← Load Mem[101]

R2 ← Load #42

R2 ← Mul R1, R2

$R0 \leftarrow Add R2, R0$

Store R0  $\rightarrow$  Mem[100]

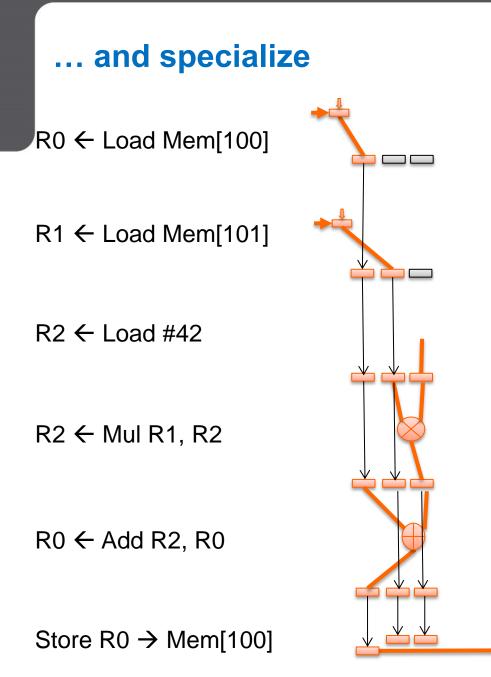

# ... and specialize by position

R0 ← Load Mem[100]

$R1 \leftarrow Load Mem[101]$

R2  $\leftarrow$  Load #42

R2 ← Mul R1, R2

$R0 \leftarrow Add R2, R0$

1. Instructions are fixed. Remove "Fetch"

## ... and specialize

R0  $\leftarrow$  Load Mem[100]

R1 ← Load Mem[101]

R2 ← Load #42

R2 ← Mul R1, R2

$R0 \leftarrow Add R2, R0$

Store R0  $\rightarrow$  Mem[100]

- 1. Instructions are fixed. Remove "Fetch"

- 2. Remove unused ALU ops

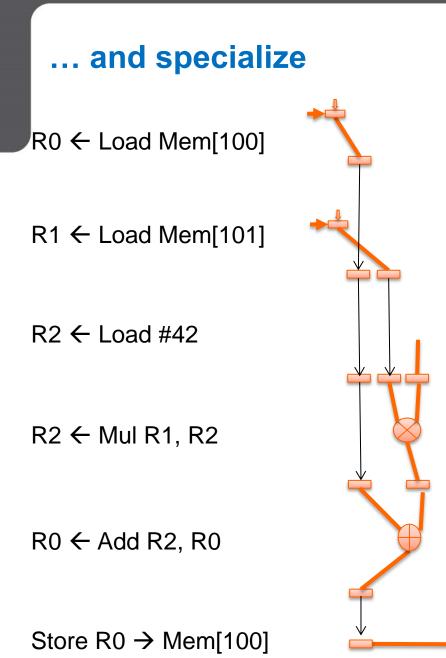

## ... and specialize

R0  $\leftarrow$  Load Mem[100]

R1 ← Load Mem[101]

R2 ← Load #42

R2 ← Mul R1, R2

$R0 \leftarrow Add R2, R0$

Store R0  $\rightarrow$  Mem[100]

- 1. Instructions are fixed. Remove "Fetch"

- 2. Remove unused ALU ops

- 3. Remove unused Load / Store

- 1. Instructions are fixed. Remove "Fetch"

- 2. Remove unused ALU ops

- 3. Remove unused Load / Store

- 4. Wire up registers properly! And propagate state.

- 1. Instructions are fixed. Remove "Fetch"

- 2. Remove unused ALU ops

- 3. Remove unused Load / Store

- 4. Wire up registers properly! And propagate state.

- 5. Remove dead data.

# **Optimize the Datapath**

R0 ← Load Mem[100]

R1 ← Load Mem[101]

R2 ← Load #42

$R2 \leftarrow Mul R1, R2$

$R0 \leftarrow Add R2, R0$

#### Store R0 $\rightarrow$ Mem[100]

- 1. Instructions are fixed. Remove "Fetch"

- 2. Remove unused ALU ops

- 3. Remove unused Load / Store

- 4. Wire up registers properly! And propagate state.

- 5. Remove dead data.

- 6. Reschedule!

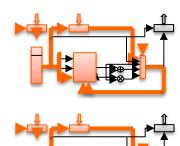

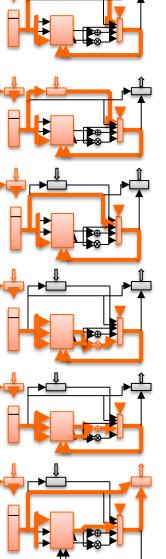

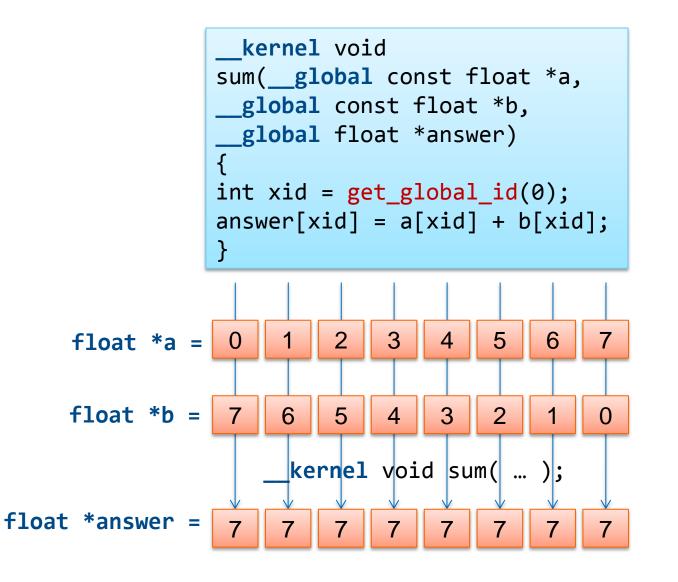

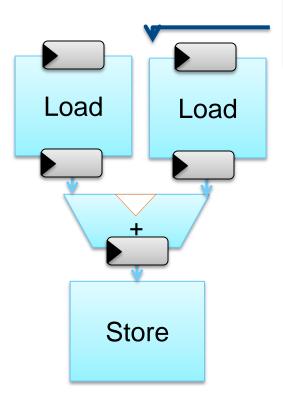

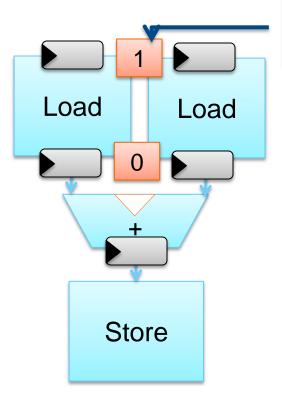

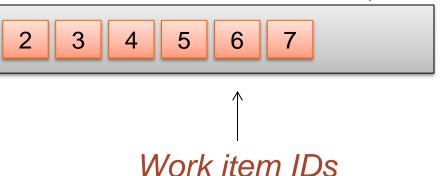

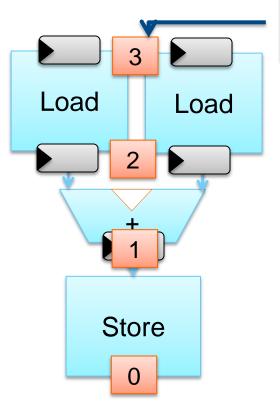

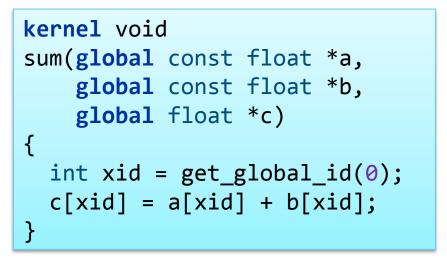

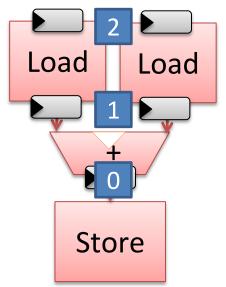

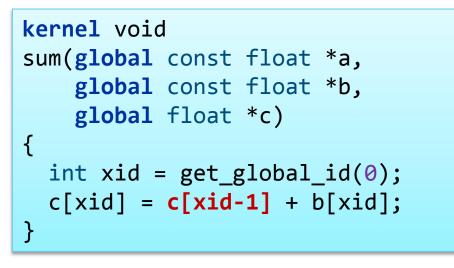

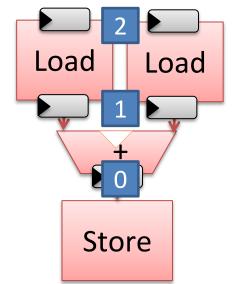

#### **Data parallel kernel**

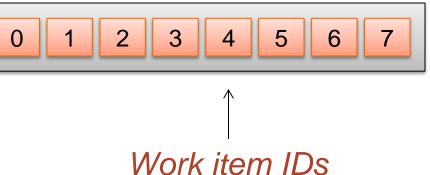

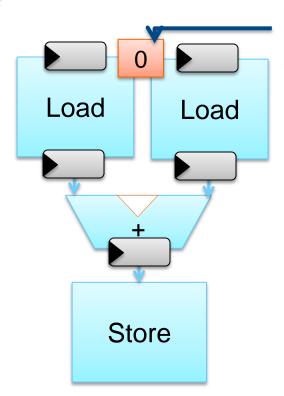

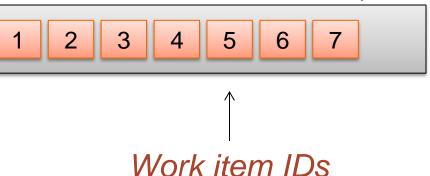

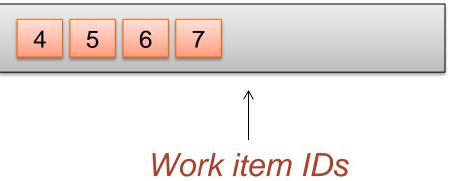

8 work items for vector add example

On each cycle the portions of the datapath are processing different threads

While thread 2 is being loaded, thread 1 is being added, and thread 0 is being stored

18

8 work items for vector add example

On each cycle the portions of the datapath are processing different threads

While thread 2 is being loaded, thread 1 is being added, and thread 0 is being stored

8 work items for vector add example

- On each cycle the portions of the datapath are processing different threads

- While thread 2 is being loaded, thread 1 is being added, and thread 0 is being stored

8 work items for vector add example

- On each cycle the portions of the datapath are processing different threads

- While thread 2 is being loaded, thread 1 is being added, and thread 0 is being stored

#### 8 work items for vector add example

- On each cycle the portions of the datapath are processing different threads

- While thread 2 is being loaded, thread 1 is being added, and thread 0 is being stored

How does my pipeline look like, how well is it performing, and are its bottlenecks?

# 2. Area

now part of Intel

#### Area

# FPGA area is multi-dimensional:

- Registers

- Look-Up Tables (LUTs)

- On-chip RAM blocks

- Dedicated Signal Processing (DSP) blocks

Each FPGA model provides a different mix of these four types of resources.

Each design demands a different mix of these four types.

#### **Importance of Area**

Area on an FPGA is major concern:

- Higher area  $\rightarrow$  fewer kernels per chip

- − Higher area → no-fit

- Higher area  $\rightarrow$  more expensive chip

- − Higher area → higher dynamic power

# How much area does a kernel use and where does it go?

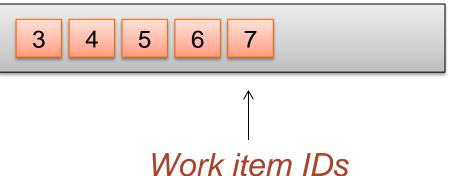

## **Area Report Detail**

For area report to be actionable, it must be done on a sub-line level.

```

float_cache[li] = global_int_data[gi+i];

```

Operations that consume area from the line above:

```

float_cache[li] = // Store to loc

(float) // Implicit int-to

global_int_data[] // Global load

gi+i // Integer add

```

// Store to local memory

// Implicit int-to-float conversion

// Global load

// Integer addition

# 3. Loop Pipelining

now part of Intel

#### **Data-Parallel Execution**

On the FPGA, we use pipeline parallelism to achieve acceleration

Threads execute in an embarrassingly parallel manner.Ideally, all parts of the pipeline are active at the same time.

## **Data-Parallel Execution - drawbacks**

Difficult to express programs which have partial dependencies during execution

Would require complicated hardware and new language semantics to describe the desired behavior

# Solution: Tasks and Loop-pipelining

Allow users to express programs as a single-thread

```

for (int i=1; i < n; i++) {

c[i] = c[i-1] + b[i];

}</pre>

```

Pipeline parallelism still leveraged to efficiently execute loops in Altera's OpenCL

In the secure loops in the secure loops

- Parallel execution inferred by compiler

- Loop Pipelining

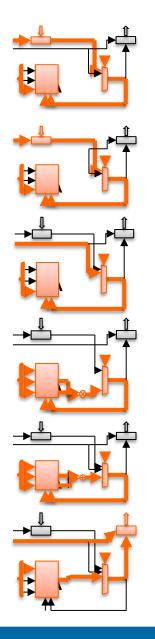

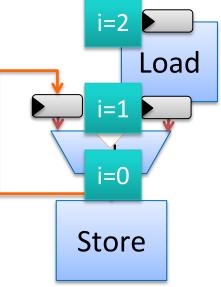

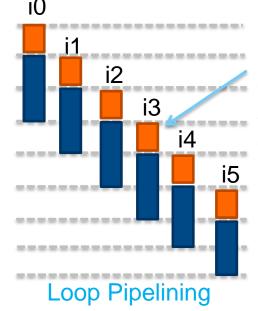

# Loop Pipelining Example

# With Loop Pipelining

#### No Overlap of Iterations!

#### Finishes Faster because Iterations Are Overlapped

now part of Inte

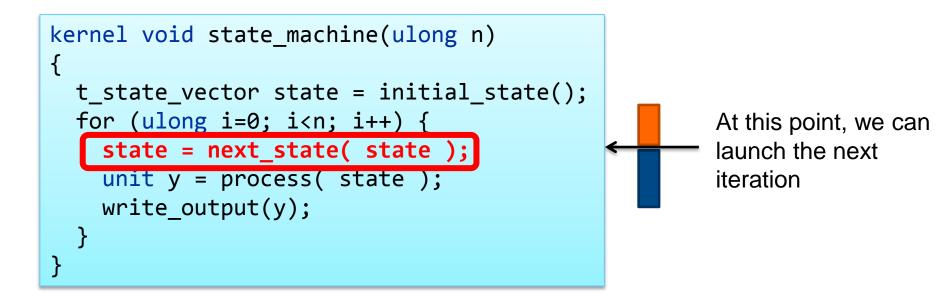

Loop Pipelining enables Pipeline Parallelism AND the communication of state information between iterations.

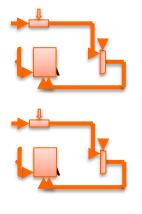

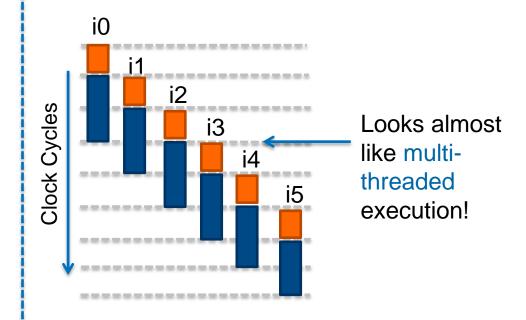

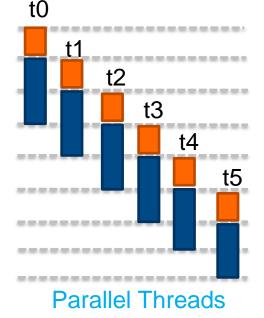

# **Parallel Threads vs. Loop Pipelining**

So what's the difference NDRange and loop pipelining?

Parallel threads launch 1 thread per clock cycle in pipelined fashion

Sometimes loop iterations cannot be started every cycle.

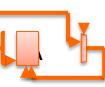

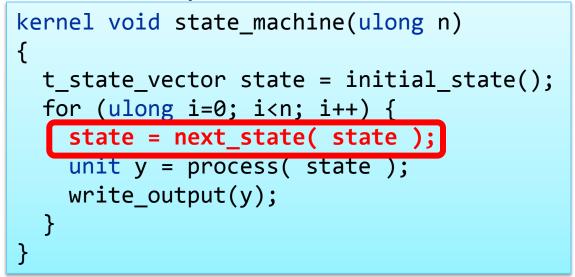

# **Loop-Carried Dependencies**

Loop-carried dependencies are dependencies where one iteration of the loop depends upon the results of another iteration of the loop

The variable state in iteration 1 depends on the value from iteration 0. Similarly, iteration 2 depends on the value from iteration 1, etc.

# **Loop-Carried Dependencies**

- To achieve acceleration, we pipeline each iteration of a loop with loop-carried dependencies

- Analyze any dependencies between iterations

- Schedule these operations

- Launch the next iteration as soon as possible

## **Trouble with Loop-Carried Dependencies**

Many things can go wrong with loop pipelining:

- Loop-carried dependency takes too long to compute.

- Loop with externally-visible events has iterations that get out of order.

- Loop may have sub-loops with iterations that get out of order.

# How well is each loop pipelined, are there any loop-carried dependency issues, and how to fix them?

# **Local Memory Flexibility**

now part of Intel

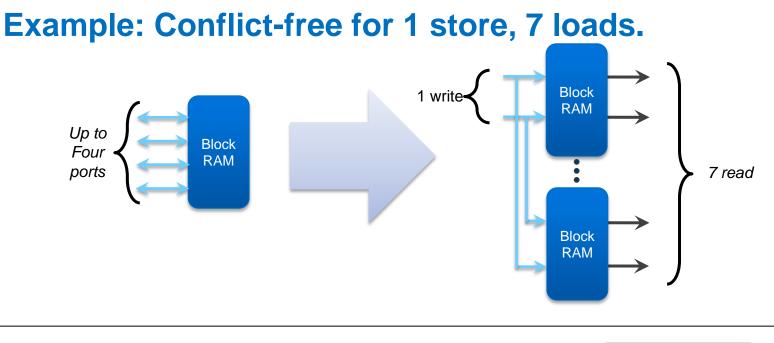

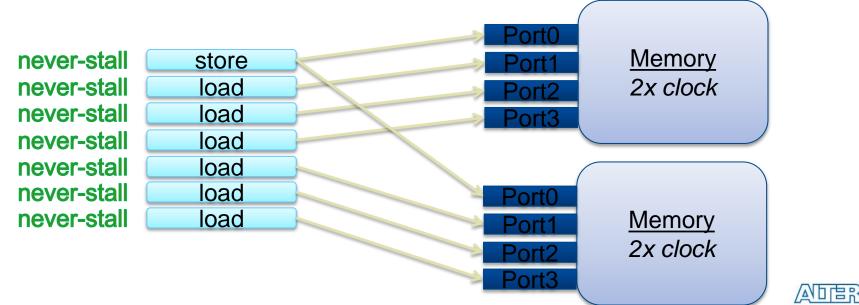

# **FPGA On-chip memory systems**

- "Local" and some "private" memories use on-chip block RAM resources

- Very high bandwidth, true random access.

- All memory system parameters are customized to <u>your</u> <u>application</u> to eliminate or minimize access contention:

- Width, depth, number of banks, port-to-bank assignment, etc.

- Caveat: Compiler has to understand access patterns to properly configure a local memory system.

now part of Intel

#### **Local Memory Feedback**

# Is my local memory efficient, how and why the compiler configured it, and what can I do to fix any inefficiencies?

# **Altera SDK for OpenCL Tools**

now part of Intel

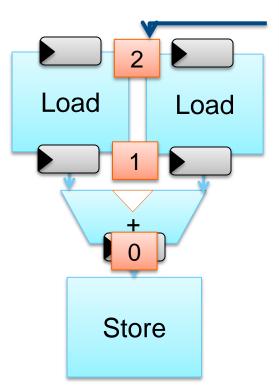

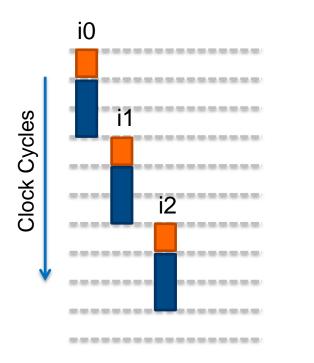

#### **Dynamic Profiler** for measuring pipeline efficiency

| Board       |                                                    | pcie385n_d5                                                      |                                |                                      |                    |                |       |

|-------------|----------------------------------------------------|------------------------------------------------------------------|--------------------------------|--------------------------------------|--------------------|----------------|-------|

| Global Memo | ry BW (MEMORY)                                     |                                                                  |                                |                                      |                    |                |       |

| Source Code | Kernel Execution matrixMul                         |                                                                  |                                |                                      |                    | Memory ban     | ndwid |

| Line #      | Source Code                                        | Attributes                                                       | Stall%                         | Occupancy%                           | Bandwidth          | demand of a lo |       |

| 64          | a <= aEnd;                                         |                                                                  |                                |                                      |                    |                |       |

| 5           | a += aStep, b += bStep) {                          |                                                                  | How often this u               | unit                                 |                    |                |       |

| 6           |                                                    |                                                                  | stalls the pipelin             | 20                                   |                    |                |       |

| 7           | // Load the matrices from device memory            |                                                                  |                                |                                      |                    |                |       |

| 8           | // to shared memory; each thread loads             |                                                                  |                                |                                      |                    |                |       |

| 59          | // one element of each matrix                      |                                                                  |                                |                                      |                    |                |       |

| 70          | AS(ty, tx) = A[a + uiWA * ty + tx];                | 0:global{MEMORY},r                                               |                                | 0:95.9%                              | 0: 1398.5MB/s, 10  |                |       |

| 71          | BS(ty, tx) = B[b + uiWB * ty + tx];                | 0:global{MEMORY},r                                               | ead 0:0.08%                    | 0:95.9%                              | 0: 10.1MB/s, 100.0 | 00%Efficiency  |       |

| 72<br>73    | "Oversharping to exclusion the matrices and loaded |                                                                  |                                |                                      |                    |                |       |

| 73<br>74    |                                                    | nize to make sure the matrices are loaded 70:global{MEMORY},read |                                |                                      |                    |                |       |

| 74<br>75    | barrier(CLK_LOCAL_MEM_FENCE);                      | Cache Hits: 99.9%<br>Non-aligned Accesses: 0.0%                  |                                |                                      |                    |                |       |

| 76          | #pragma unroll                                     |                                                                  | 1.1                            | the second state of the second state |                    |                |       |

| 76          | for (int k = 0; k < BLOCK_SIZE; ++k) {             | Memo                                                             | ry site coalesced with other r | nemory sites.                        | HOW 0              | ften this unit |       |

| 78          | Csub += AS(ty, k) * BS(k, tx);                     | 0: _local,ead                                                    | 0: 0.0%                        | 0:95.9%                              | does               | useful work.   |       |

| 79          |                                                    | UIUCal eau                                                       | 0.0.070                        | 0. 33.970                            | 0003               |                |       |

| 80          | 3                                                  |                                                                  |                                |                                      |                    |                |       |

| 31          | // Synchronize to make sure that the preceding     |                                                                  |                                |                                      |                    |                |       |

| 32          | // computation is done before loading two new      |                                                                  |                                |                                      |                    |                |       |

| 83          | // sub-matrices of A and B in the next iteration   |                                                                  |                                |                                      |                    |                |       |

| 84          | barrier(CLK_LOCAL_MEM_FENCE);                      |                                                                  |                                |                                      |                    |                |       |

| 85          | canter(cert_coone_mem_renter),                     |                                                                  |                                |                                      |                    |                |       |

Pipeline Performance Stats (collected with hardware counters)

| Area Report                                                                                                                                                                                                                                                                                              |                                                 |           | Break down Area<br>utilization into BSP,<br>global interconnect,<br>kernels, and line<br>numbers. |           | local men | e suggestions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 #define NUM_READS 8                                                                                                                                                                                                                                                                                    | Area Report<br>(area utilization values are est | materl    |                                                                                                   |           |           | configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 2 #define NUM WRITES 8                                                                                                                                                                                                                                                                                   | larca utilization values are est                |           | FFs                                                                                               | RAMs      | DSPs      | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 3                                                                                                                                                                                                                                                                                                        | System Total (Logic: 15%)                       | LEs       | 64399 (6%)                                                                                        |           |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4                                                                                                                                                                                                                                                                                                        |                                                 |           |                                                                                                   | 387 (15%) | 0 (0%)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5attribute((reqd_work_group_size(1024,1,1))                                                                                                                                                                                                                                                              | Board interface                                 | 38262     | 44528                                                                                             | 257       | 0         | Platform interface logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 6 kernel void big_Imem (global int* restrict in,                                                                                                                                                                                                                                                         | Global interconnect                             | 5034      | 9568                                                                                              | 52        | 0         | <ul> <li>Global interconnect for 1 global load<br/>and 1 global store.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 7 global int* restrict out) {                                                                                                                                                                                                                                                                            | big_lmem (Logic: 2%)                            | 6212 (1%) | 10303 (1%)                                                                                        | 78 (3%)   | 0 (0%)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 8                                                                                                                                                                                                                                                                                                        | Function overhead                               | 1628      | 1799                                                                                              | 0         | 0         | Kernel dispatch logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| <pre>9 local int Imem[1024];<br/>10 int gi = get_global_id(0);<br/>11 int gs = get_global_size(0);<br/>12 int li = get_local_id(0);<br/>13 int res = in[gi];<br/>14 #pragma unroll<br/>15 for (int i=0; i<num_writes; i++)="" {<br="">16 Imem[li - i] = res;<br/>17 res &gt;&gt;= 1;</num_writes;></pre> | b.cl:9 (Imem)                                   | 132       | 1024                                                                                              | 8         | 0         | <ul> <li>Local memory: Potentially inefficient<br/>configuration.<br/>Requested size 4096 bytes (rounded<br/>up to nearest power of 2), implemented<br/>size 8192 bytes, replicated 2 times<br/>total, stallable, 8 reads and 8 writes.<br/>Additional information:</li> <li>Reduce the number of write accesses<br/>or fix banking to make this memory<br/>system stall-free.</li> <li>Replicated 2 times to efficiently<br/>support multiple simultaneous<br/>workgroups. This replication resulted in<br/>no increase in actual block RAM usage.</li> <li>Banked on lowest dimension into 4<br/>separate banks (this is a good thing).</li> </ul> |  |

| 18 }                                                                                                                                                                                                                                                                                                     | Block0 (Logic: 1%)                              | 4452 (1%) | 7480 (1%)                                                                                         | 70 (3%)   | 0 (0%)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 19 barrier(CLK_GLOBAL_MEM_FENCE);                                                                                                                                                                                                                                                                        | State                                           | 64        | 64                                                                                                | 0         | 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 20 res = 0;                                                                                                                                                                                                                                                                                              | b.cl:13                                         | 358       | 497                                                                                               | 13        | 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 21 #pragma unroll                                                                                                                                                                                                                                                                                        | b.cl:16                                         | 779       | 2591                                                                                              | 8         | 0         | <ul> <li>Stallable write to memory declared on<br/>b.cl:9.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| <pre>22 for (int i=0; i &lt; NUM_READS; i++) { 23 res ^= Imem[Ii - i];</pre>                                                                                                                                                                                                                             | b.cl:17                                         | 25        | 25                                                                                                | 0         | 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| <pre>23 res ^= Imem[li - i];<br/>24 }<br/>25 out[gi] = res;<br/>26 }<br/>© 2016 Altera—Public</pre>                                                                                                                                                                                                      |                                                 |           |                                                                                                   |           |           | ses to local<br>are described,<br>their stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### **Optimization Report** for Loop Pipelining Feedback

Loop Report:

+ Loop "Block1" (file a.cl line 2)

Pipelined with successive iterations launched every 324 cycles due to:

Memory dependency on Load Operation from: (file a.cl line 3)

Store Operation (file a.cl line 3)

Largest Critical Path Contributors:

49%: Load Operation (file a.cl line 3)

49%: Store Operation (file a.cl line 3)

# **Thank You**

now part of Intel