# INTEGRATING OPENCL<sup>™</sup> KERNELS INTO THE PROGRAM FLOW

Alexei Katranov

IWOCL '16, April 21, 2016, Vienna, Austria

# Hardware: customization, integration, heterogeneity

Multicore CPU + integrated units for graphics, media and compute Discrete co-processors and accelerators FPGAs, fixed function devices, domain-specific compute engines, etc...

Diverse and heterogeneous environments with multiple compute resources

#### Optimization Notice

# Intel® Threading Building Blocks (Intel® TBB)

- Widely used C++ template library

- Rich feature set for general purpose parallelism

- For Windows\*, Linux\*, OS X\*, Android\*, etc.

- Both commercial and open-source licenses

- Commercial support for Intel<sup>®</sup> Atom<sup>™</sup>, Core<sup>™</sup>, Xeon<sup>®</sup> processors, and for Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessors

- Community contributions for non-Intel architectures

http://software.intel.com/intel-tbb http://threadingbuildingblocks.org

#### Optimization Notice

# **Rich Feature Set for Parallelism**

Parallel algorithms and data structures

Threads and synchronization

Memory allocation and task scheduling

| Generic Parallel                                                                                | Flow Graph                                                                                                 | Concu                                                                                    | rrent Conta        | ainers                                         |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------|------------------------------------------------|--|

| Algorithms<br>Efficient scalable way                                                            | A set of classes to<br>express parallelism<br>as a graph of<br>compute<br>dependencies and/or<br>data flow | Concurrent access, and a scalable alternative to serial containers with external locking |                    |                                                |  |

| to exploit the power<br>of multi-core without<br>having to start from<br>scratch                |                                                                                                            | Synchronization Primitives                                                               |                    |                                                |  |

|                                                                                                 |                                                                                                            | Atomic operations, a variety of mutexes with different properties, condition variables   |                    |                                                |  |

| Task Scheduler                                                                                  |                                                                                                            | Thread Local<br>Storage                                                                  | Threads            | Miscellaneous                                  |  |

| Sophisticated work scheduling engine<br>that empowers parallel algorithms<br>and the flow graph |                                                                                                            | Unlimited number<br>of thread-local<br>variables                                         | OS API<br>wrappers | Thread-safe<br>timers and<br>exception classes |  |

| Memory Allocation                                                                               |                                                                                                            |                                                                                          |                    |                                                |  |

| Scalable memory manager and false-sharing free allocators                                       |                                                                                                            |                                                                                          |                    |                                                |  |

|                                                                                                 |                                                                                                            |                                                                                          |                    |                                                |  |

Copyright © 2016, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others. íntel

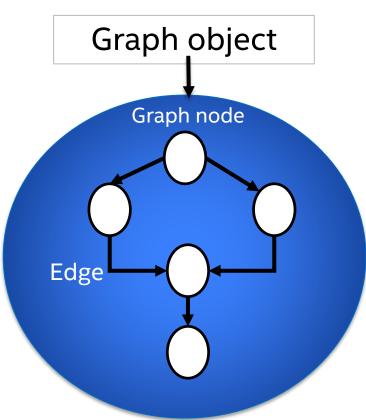

# Intel TBB Flow Graph at glance

- Intel TBB Flow Graph is an abstraction built on top of TBB task scheduler API

- Like an additional programming model

- Explicitly defined control and data dependencies between computations

- Parallelism is automatically extracted

- Intel TBB flow graph is targeted to multicore shared memory systems.

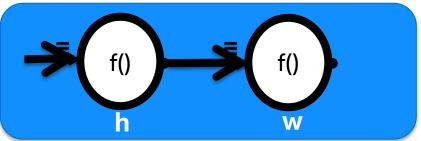

# Hello World Example

# Users create nodes and edges, interact with the graph and wait for it to complete

```

tbb::flow::graph g;

tbb::flow::continue_node< tbb::flow::continue_msg >

h( g, []( const continue_msg & ) { std::cout << "Hello "; } );

tbb::flow::continue_node< tbb::flow::continue_msg >

w( g, []( const continue_msg & ) { std::cout << "World\n"; } );

tbb::flow::make_edge( h, w );

h.try put(continue msg());

```

g.wait for all();

# **COMBINING OPENCL<sup>™</sup> AND INTEL TBB**

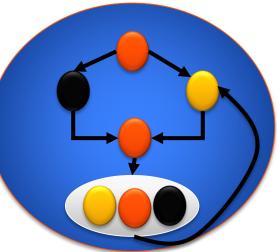

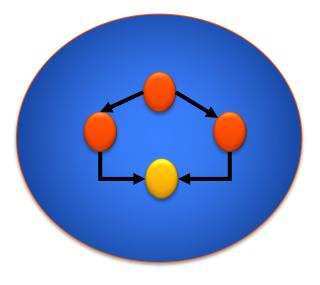

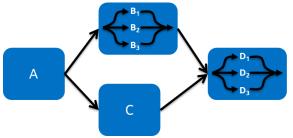

# Idea of Heterogeneous Flow Graph

- TBB flow graph as a coordination layer

- Be the glue that connects hetero HW and SW IP together

- Expose parallelism between blocks; simplify integration

Copyright © 2016, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

**Optimization Notice**

# OpenCL<sup>™</sup> node

#### Core functionality:

- enumerate & query OpenCL<sup>™</sup> devices

- select a device to be used for program execution

- transfer data to/from the device

- execute a given kernel there

- support efficient kernel chaining (no excessive data transfer)

OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission by Khronos.

## Hello World example for OpenCL node

```

// A graph with OpenCL support.

opencl_graph g;

```

```

const char str[] = "Hello, World!";

// OpenCL buffer for the string

opencl_buffer<cl_char> b(g, sizeof(str));

// Copy the string to the buffer

std::copy n(str, sizeof(str), b.begin());

```

// A node that outputs the content of an incoming buffer

opencl\_node<tuple<opencl\_buffer<cl\_char>>> clPrint(g, "hello\_world.cl", "print");

k.set\_ndranges({1});

```

// Send the buffer as the node input

input_port<0>(clPrint).try_put(b);

// Wait for work completeion.

g.wait for all();

```

```

// hello_world.cl

kernel void print( global char *str ) {

printf("OpenCL says '");

for ( ; *str; ++str ) printf("%c", *str);

printf("'\n");

```

#### Optimization Notice

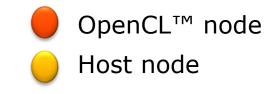

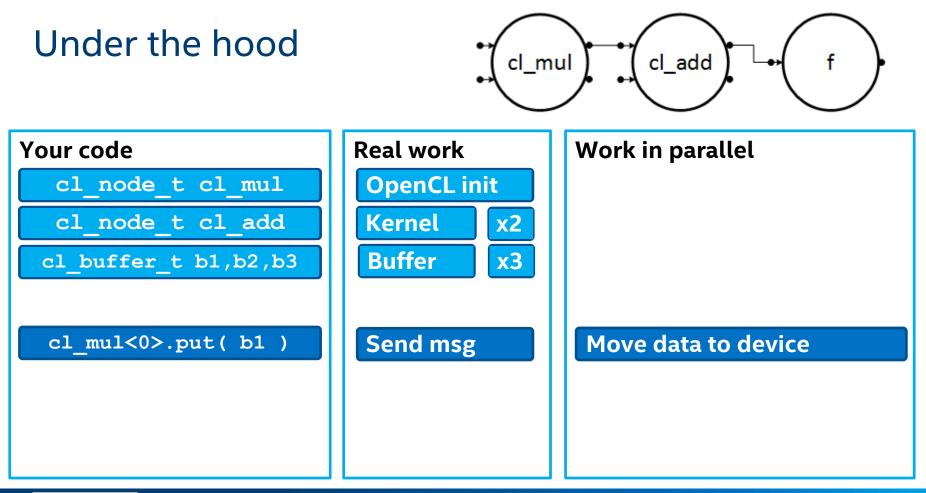

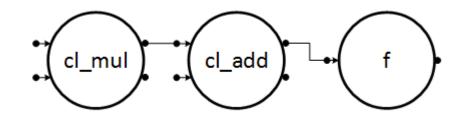

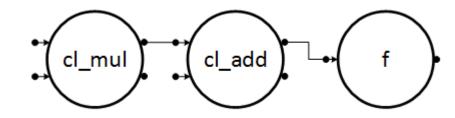

## OpenCL node pipeline example

# OpenCL node pipeline example

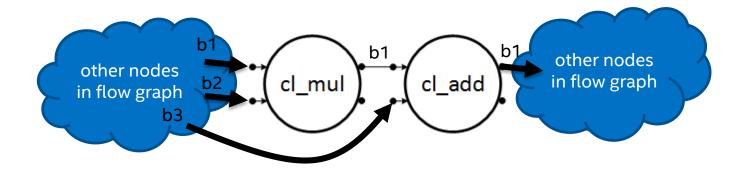

typedef opencl\_buffer<cl\_int> cl\_buffer\_t;

typedef opencl\_node < tuple<cl\_buffer\_t, cl\_buffer\_t> > cl\_node\_t;

#### // Create nodes

```

cl_node_t cl_mul( g, "program.cl", "mul" );

cl_node_t cl_add( g, "program.cl", "add" );

function node t f( g, unlimited, []( const cl buffer t &t ) {...} );

```

```

// Create dependencies between nodes

make_edge( cl_mul, cl_add );

make_edge( cl_add, f );

```

```

// Put buffers to the graph

cl_buffer_t bl(g, N), b2(g, N), b3(g, N);

input_port<0>( cl_mul ).try_put( b1 );

input_port<1>( cl_mul ).try_put( b2 );

input_port<1>( cl_add ).try_put( b3 );

```

#### **Optimization Notice**

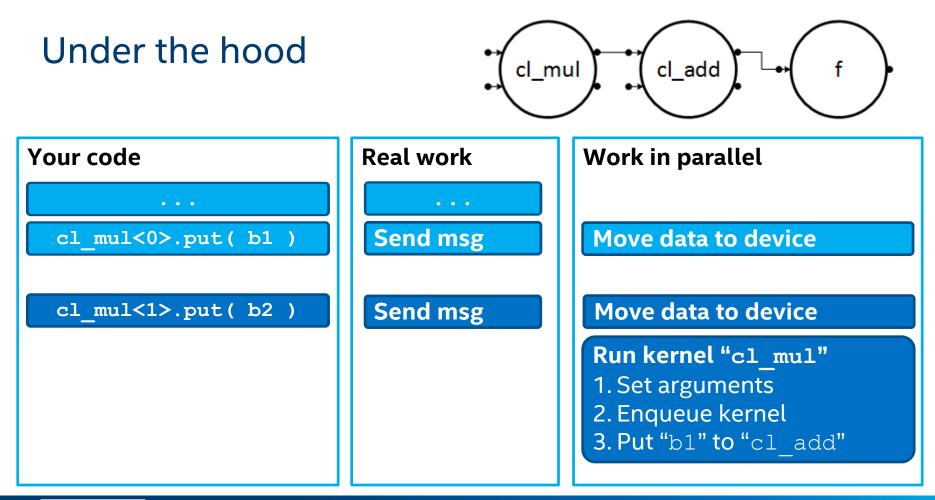

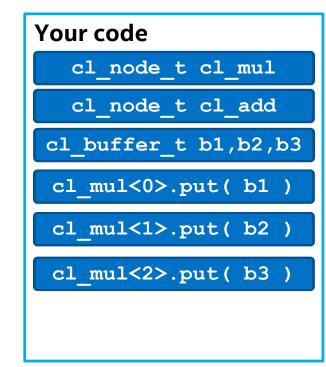

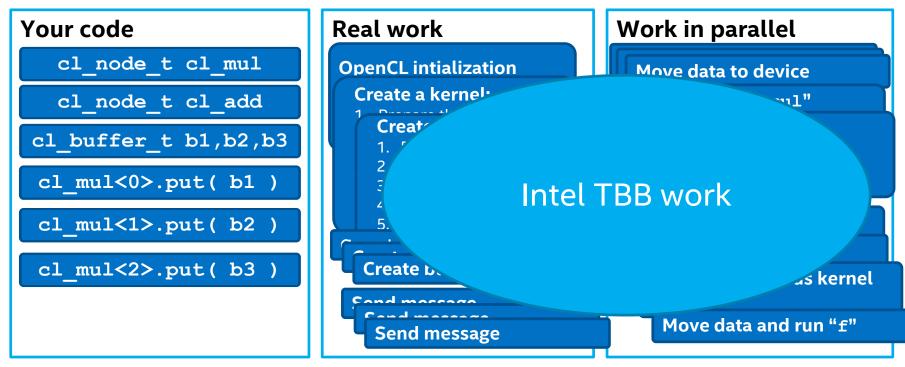

#### Your code

cl node t cl mul

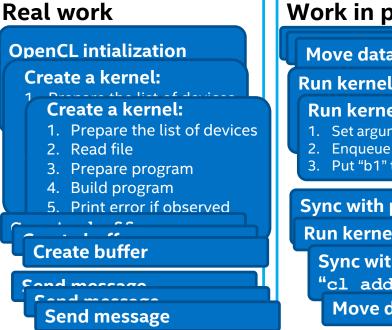

#### **Real work**

#### **OpenCL intialization**

- 1. Query the available devices

- 2. Create context

- 3. Create queue

#### Create a kernel:

- 1. Prepare the list of devices

- 2. Read file

- 3. Prepare program

- 4. Build program

- 5. Print error if observed

- 6. Get a kernel

#### **Optimization Notice**

| Your code        | Real work            |

|------------------|----------------------|

| cl_node_t cl_mul | OpenCL intialization |

|                  | Create a kernel      |

| cl_node_t cl_add | Create a kernel      |

|                  |                      |

|                  |                      |

|                  |                      |

|                  |                      |

#### Optimization Notice

| Your code            | Real work            |

|----------------------|----------------------|

| cl_node_t cl_mul     | OpenCL intialization |

| cl_node_t cl_add     | Create a kernel      |

|                      | Create a kernel      |

| cl_buffer_t b1,b2,b3 | Create a buffer      |

|                      | Create a buffer      |

|                      | Create a buffer      |

|                      |                      |

#### **Optimization Notice**

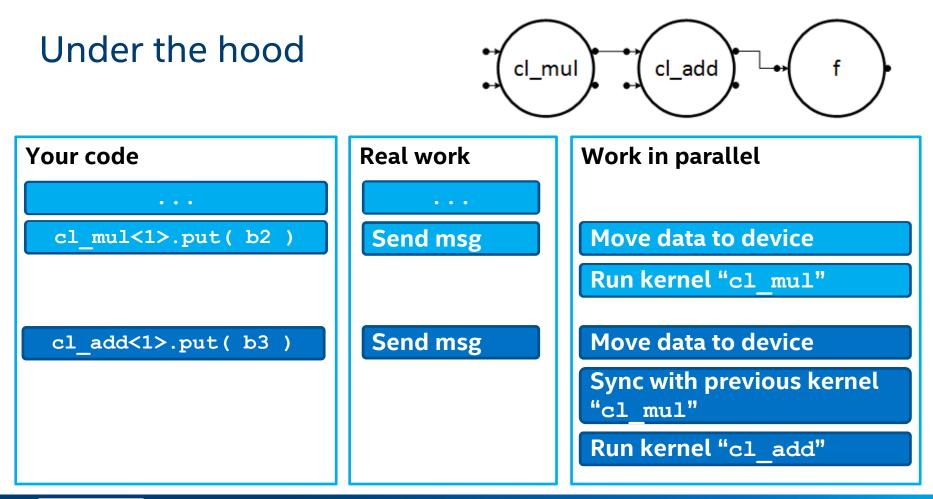

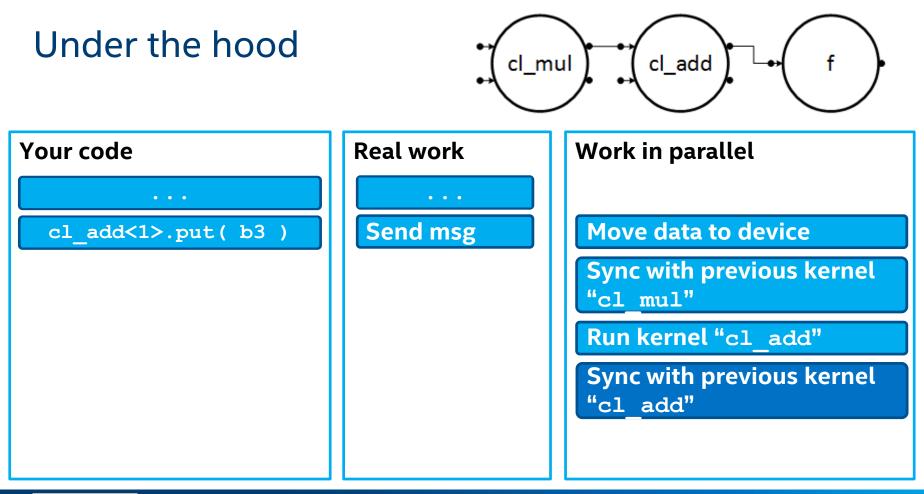

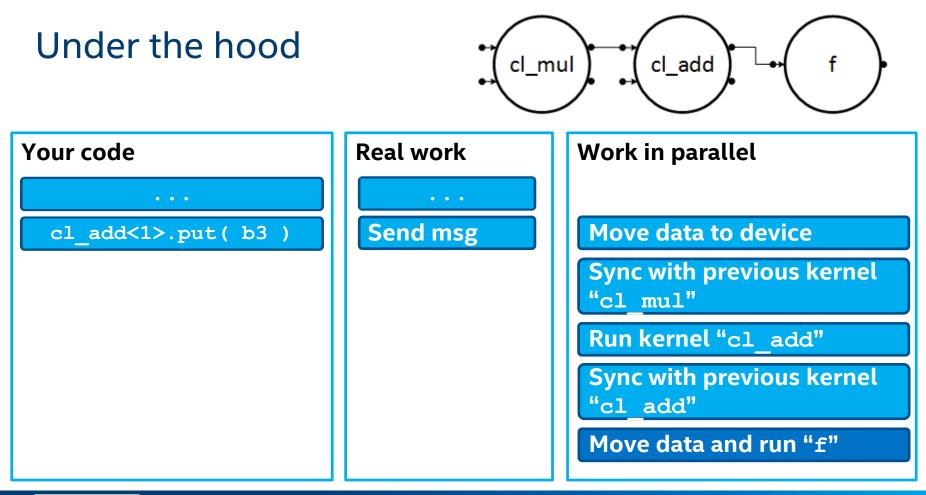

### Work in parallel

#### Move data to device

Run kernel "cl mul"

Run kernel "cl add"

- 1. Set arguments

- 2. Enqueue kernel

- 3. Put "b1" to "cl add"

#### Sync with previous kernel

Run kernel "cl add"

Sync with previous kernel "cl add"

Move data and run "f"

#### **Optimization Notice**

#### Optimization Notice

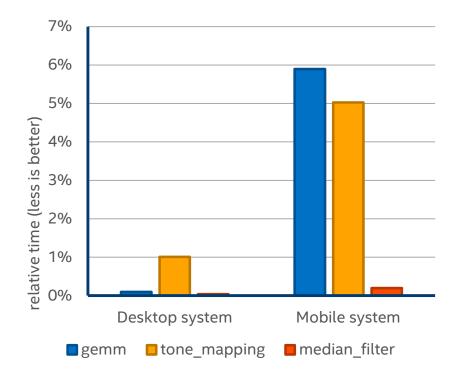

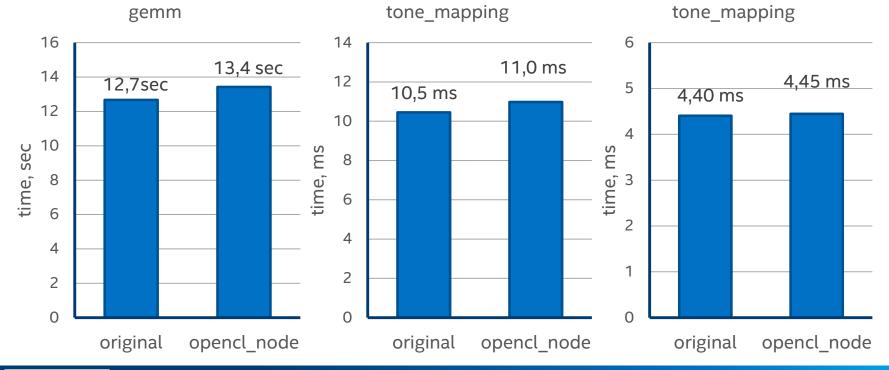

# **PERFORMANCE EVALUATION**

# **OpenCL** node overheads

#### Configuration info:

Desktop system: Hardware: Intel® Core™ i7-6700K CPU @4.00Ghz, 16 GB RAM; Software: Microsoft\* Windows 10 Enterprise, Microsoft Visual Studio\* Professional 2015 Update 1, Intel HD Graphics Driver for Windows 15.40.

Mobile system: Intel Core i5-4300U CPU @1.90Ghz, 8 GB RAM; Software: Microsoft Windows 8.1 Enterprise, Microsoft Visual Studio Professional 2015 Update 2, Intel HD Graphics Driver for Windows 15.36

# **OpenCL node overheads in detail**

Mobile system

Desktop system

**Optimization Notice**

Copyright © 2016, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others. íntel

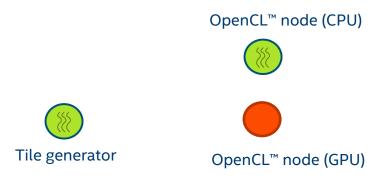

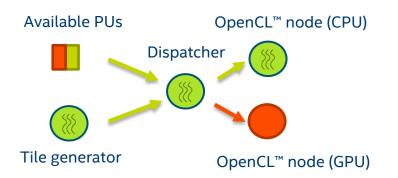

# Load balancing CPU and GPU

Generic support makes coordinating with any model easier and efficient

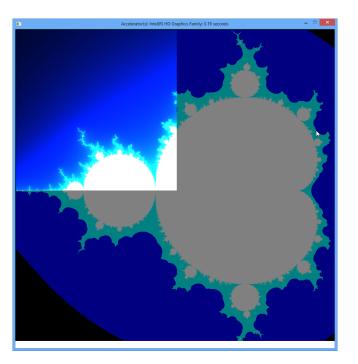

# - 🗆 🗙 Accelerator(s): Intel(R) HD Graphics Family: 3.19 second:

#### **Optimization Notice**

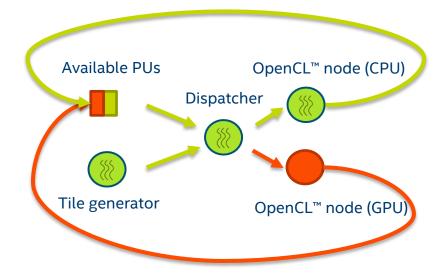

# Load balancing CPU and GPU

Generic support makes coordinating with any model easier and efficient

#### intel

#### Copyright © 2016, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

**Optimization Notice**

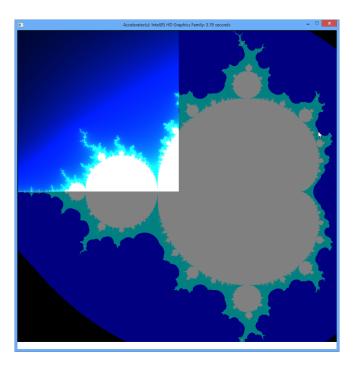

## Load balancing CPU and GPU

Generic support makes coordinating with any model easier and efficient

#### **Optimization Notice**

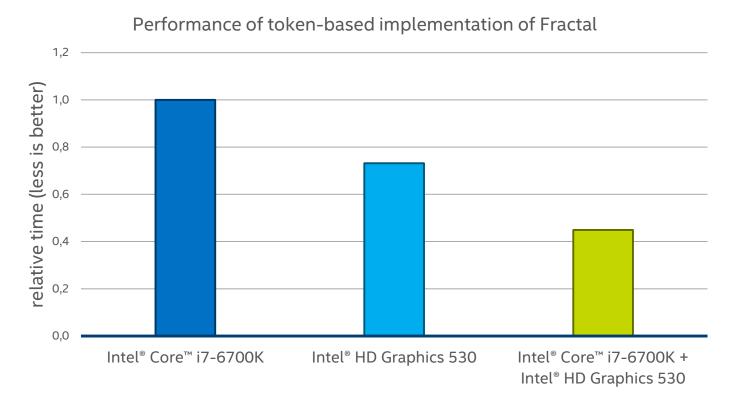

# Load balancing CPU and GPU: performance

Copyright © 2016, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

**Optimization Notice**

# SUMMARY

Intel TBB flow graph is a coordination layer on heterogeneous systems:

- First class support for OpenCL (opencl\_node overview: <u>https://software.intel.com/en-us/blogs/2015/12/09/opencl-node-overview</u>)

- Reasonable performance overheads (about 1% for 4 ms workload on a desktop system)

- Declarative "language" to express unstructured parallelism, e.g. token-based balancing scheme

Intel TBB is open source and freely available on

https://www.threadingbuildingblocks.org/

# Acknowledgments

Our thanks to

- Alexey Kukanov for co-authoring and thorough review

- Michael Voss for material contribution to the features described in this presentation

- Robert Ioffe for evaluating our work and providing valuable feedback

- Others who helped in developing the functionality

32

# Legal Disclaimer & Optimization Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Copyright © 2016, Intel Corporation. All rights reserved. Intel, Pentium, Xeon, Xeon Phi, Core, VTune, Cilk, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804

# Backup: Motivation for data flow and graphparallelism Serial implementation (perhaps vectorized)

x = A(); y = B(x); z = C(x);D(y,z);

Loop-parallel implementation

Loop- and graph-parallel implementation

#### **Optimization Notice**