## **IWOCL 2024**

The 12th International Workshop on OpenCL and SYCL

#### Intel® SHMEM: an OpenSHMEM Runtime with GPUinitiated Operations using SYCL

Lawrence Stewart, Intel Corporation David Ozog, Md. Wasi-ur- Rahman, Lawrence Stewart

APRIL 8-11, 2024 | CHICAGO, USA | IWOCL.ORG

#### Legal Disclosures

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Intel provides these materials as-is, with no express or implied warranties.

Performance varies by use, configuration and other factors. Learn more at www.Intel.com/PerformanceIndex. Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure. See backup for configuration details. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks

This document contains information on products in the design phase of development which Intel may change at any time without notice. Do not finalize a design with this information. Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks.

Intel<sup>®</sup>, Intel logo and Xeon<sup>®</sup> are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Other names and brands may be claimed as the property of others.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at [intel.com].

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

WARNING - This document contains technical data whose export is restricted by the Arms Export Control Act (Title 22, U.S.C., Sec 2751, etq.) or the Export Administration Act of 1979, as amended, Title 50, U.S.C., App. 2401 et seq. Violations of these export laws are subject to severe criminal penalties. Disseminate in accordance with provisions of DoD Directive 5230.25.

Copyright © 2024 Intel Corporation.

### Outline

- Overview

- PGAS and OpenSHMEM

- Background

- Current State and Future Directions

- Intel<sup>®</sup> SHMEM

- Release 1.0.0

- Intel<sup>®</sup> SHMEM with SYCL

- Performance

- OneCCL and Intel<sup>®</sup> MPI

#### Overview

- What is Intel<sup>®</sup> SHMEM?

- A library for one-sided and collective communication

- Implements the OpenSHMEM API, with extensions for GPU

- Operations Supported

- Remote memory access, remote atomic memory operations, collective operations, synchronization of multiple processing elements (ranks)

- API available on host and inside SYCL kernels (device initiated)

- Benefits

- Lightweight, high-performance communications for distributed GPU applications

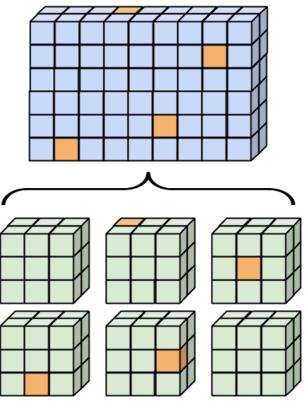

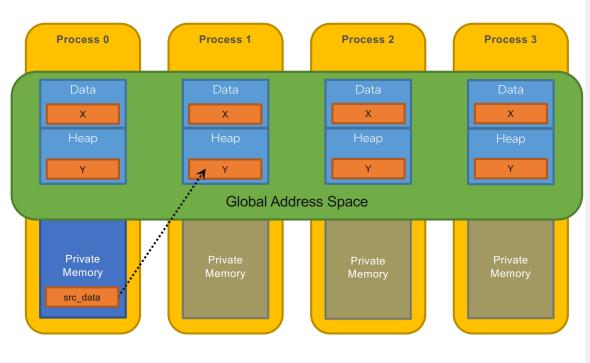

#### Partitioned Global Address Space

- Processing Elements (Pes) have access to global memory, and are aware what data is where.

- Operations:

- Put(), Get(), Add(), Put-Signal(), Barrier(), ...

- Distributed Memory model:

- "Shared" memory with a process ID

- SPMD Execution Model:

- SPMD = Same Program Multiple Data

- All PEs execute the same program

Partitioned Global Address Space (PGAS)

**Distributed Data Spaces**

5

## **OpenSHMEM:** Basic Operations

#### Initialization

shmem\_init() sets up symmetric data regions

#### Memory Managment

- "Symmetric" memory is remotely accessible

- shmem\_{malloc|calloc|realloc}

Remote Memory Access (RMA):

- Put/Get/Put-with-signal

Atomic Memory Operations (AMO):

- Add, compare-swap, fetch, bitwise, etc.

Collective Operations:

- Barrier, Broadcast, Reduce, Alltoall, etc.

## **OpenSHMEM Specification 1.5**

- Active community

- Current (1.5) features

- Threads, Teams

- Profiling Interface

- Proposed (1.6, 1.7)

- Completions

- Non-blocking collectives

- Aggregation

- GPU support

- ...

| <section-header>OpenSHMEM<br/>Application Programming Interface</section-header>                                                                                                                                                                         | Hewlett Packard   Image: Constraint of the sector   Image: Constraint of th |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8th June 2020                                                                                                                                                                                                                                            | Image: Story Brook University     Argonne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Development by<br>• For a current list of contributors and collaborators please see<br>http://www.openshimem.org/site/Contributors/<br>• For a current list of OpenSHMEM implementations and tools, please see<br>http://openshimem.org/site/Links#impl/ | *names and images may be claimed as<br>the property of others                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## GPUs and OpenSHMEM

- Distributed Multi-GPU Clusters growing quickly

- Some Intel-based systems

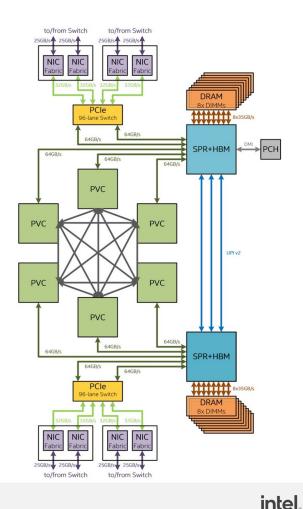

- Aurora has 12 Ponte Vecchio (PVC) GPU tiles connected w/Xe-Link, dual Sapphire Rapids (SPR)

- Dawn Phase 1<sup>1</sup>, SuperMUC-NG Phase 2<sup>2</sup>, Clementina XX1<sup>3</sup>, TACC Stampede 3

- Other GPU-initiated SHMEM libraries

- NVIDIA NVSHMEM supports OpenSHMEM 1.5 features with CUDA and NVIDIA GPU specific extensions only

- AMD ROC-SHMEM supports a subset of OpenSHMEM 1.5 APIs with HIP and AMD GPU specific extensions only

- Current OpenSHMEM standard does not enable accelerators

- Intel<sup>®</sup> SHMEM is envisioned to provide open GPU-initiated one-sided programming based on OpenSHMEM and SYCL

<sup>1</sup> https://www.intel.com/content/www/us/en/newsroom/news/intel-dell-power-uk-fastest-ai-supercomputer.html 2 https://doku.lrz.de/supermuc-ng-10745965.html 3 https://www.datacenterdynamics.com/en/tags/clementina-xxi/

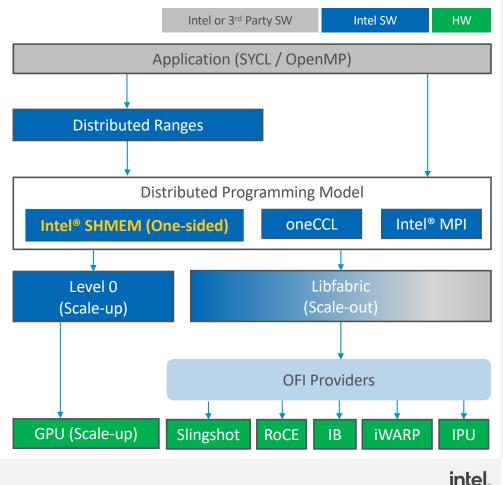

#### Intel<sup>®</sup> SHMEM

- GPU-initiated OpenSHMEM APIs on Intel Data Center GPUs using C++/SYCL

- SPMD model for developers on heterogeneous platforms

- OpenSHMEM standard device- and hostinitiated point-to-point (RMA, AMO) and collective operations

- Device Extension APIs for GPU capabilities (SYCL Groups)

- Promote adoption of GPUs into OpenSHMEM standard

- Leverage efficient host runtimes, such as Sandia OpenSHMEM, Intel<sup>®</sup> MPI, oneCCL

- Open-source release <u>1.0.0</u> is available

#### Release 1.0.0

- Open-source Release

- GitHub repo: <u>https://github.com/oneapi-src/ishmem</u>

- Specification: <u>https://oneapi-src.github.io/ishmem/intro.html</u>

- Tested on Intel<sup>®</sup> Data Center Max Series GPUs with

- Xe-Link (intra-node)

- CXI/Verbs;RXM OFI providers (inter-node)

- Major Features

- RMA, AMO, Collectives, Signaling, Synchronization, Memory Ordering

- Sandia OpenSHMEM as CPU-side backend (GPU heap and GPU RDMA support)

- Configurable with Unified Shared Memory host heap

- Supports fast GPU and host interaction

- Unit tests, intranode performance tests, examples

- Blog post on Intel<sup>®</sup> SHMEM: "Introducing the New Intel<sup>®</sup> SHMEM" by Rahman, Stewart, Ozog

## Intel® SHMEM with SYCL Example

| <pre>red = Intel® SHMEM blue = comment black = SYCL / C++</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>1 #include <ishmem.h><br/>#include <ishmemx.h></ishmemx.h></ishmem.h></pre>                                                                                                                                                                                                                                                            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ol> <li>Include header files</li> <li>Initialize with ishmem_init()</li> <li>Allocate symmetric objects using memory management APIs</li> <li>Query APIs can be used within the kernel to retrieve runtime info</li> <li>Within the kernel, communication APIs will be translated to load/store (intra-node) or corresponding host-based API through the proxy (inter-node)</li> <li>Device-extension APIs optimizes by utilizing all the work-items in a work-group cooperatively</li> <li>ishmem_finalize() finalizes the runtime and destroys all allocated resources</li> </ol> | <pre>int main() {     /* Initialize Intel SHMEM */     ishmem_init();     /* Allocate objects on symmetric heap */     int *src = (int *) ishmem_malloc(N * sizeof(int));     int *dst = (int *) ishmem_malloc(N * sizeof(int));     /* Launch kernel */     auto e = q.parallel_for(nd_range&lt;3&gt;(range&lt;3&gt;(x_s, y_s, z_s),</pre> |  |  |

| IWOCL 2024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                             |  |  |

#### Jacobi: 2D Stencil

- Iterative approach of solving a set of linear equations

- Each entry in the 2D matrix is computed using the surrounding elements

- Exchange of data between iterations are performed using ishmem\_float\_p

- Further optimization opportunities with device extension APIs

```

auto sum red = sycl::reduction(12 norm d, sycl::plus<>());

auto ret = q.parallel for(

sycl::range<1>{global_range}, sum_red, [=](sycl::id<1> idx,

auto &sumr) {

int iy = idx / nx + iy start;

int ix = idx \% nx + 1;

real local norm = 0.0;

if (iy < iy_end && ix < (nx - 1)) {</pre>

const real new val = (0.25) * (a[iy * nx + ix + 1] +

a[iy * nx + ix - 1] + a[(iy + 1) * nx + ix] +

a[(iy - 1) * nx + ix]);

a_new[iy * nx + ix] = new_val;

if (iy start == iy)

ishmem float p((real *) (a new + top iy * nx + ix),

new val, top pe);

if (iy end - 1 == iy)

ishmem_float_p((real *) (a_new + bottom_iy * nx + ix),

new val, bottom pe);

real residue = a[iy * nx + ix] - new val;

local_norm = residue * residue;

sumr += local norm;

}

);

```

## Performance Test Setup

- Measurements done on Intel internal Aurora validation system

- Hardware details:

- 6 Intel® Data Center GPU Max Series (PVC) devices

- 6 GPUs are fully connected by XeLink fabric

- 2x Intel<sup>®</sup> Xeon<sup>®</sup> CPU Max 9470C (SPR) CPUs

- 2.0 GHz, each socket with 52 cores and 2 threads per core

- 8x Slingshot 11 NICs (200 Gbps each)

- Software Details:

- Intel<sup>®</sup> SHMEM 1.0.0

- Sandia OpenSHMEM (main branch)

- Intel<sup>®</sup> one<sup>A</sup>PI DPC++/C++ Compiler 2024.1.0

- Measurements taken March 2024

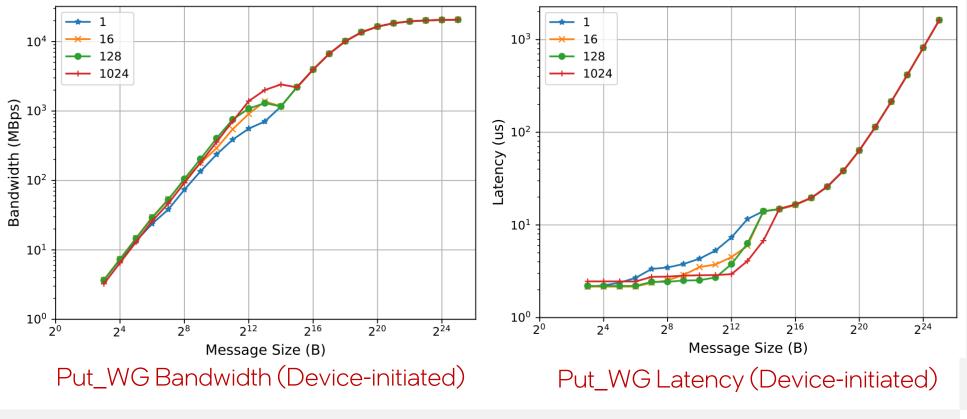

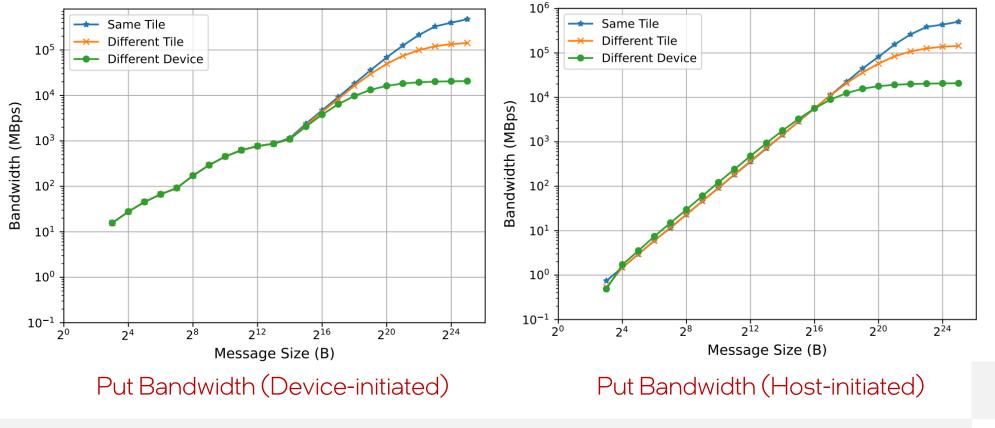

#### Performance

#### Intel<sup>®</sup> SHMEM Takeaways

- Available Now

- Opensource Release

- Light weight (low impact on source code)

- GPU and Host initiated operations on GPU memory

- Small operations are low latency

- Large operations achieve full hardware bandwidth

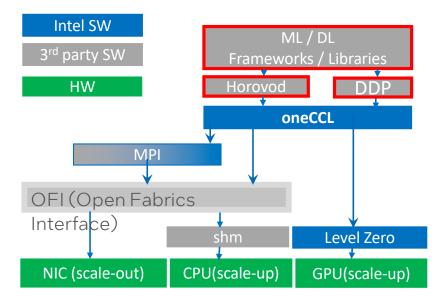

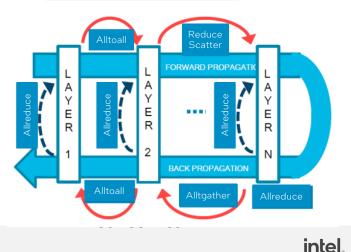

## oneCCL and Intel® MPI

intel.

#### Intel® oneAPI Collective Communications Library Key Features Supported Collectives

Enables efficient implementations of collectives used for deep learning training: all-gather, all-reduce, and more

oneCCL is designed for easy integration into deep learning (DL)

frameworks (PyTorch, TensorFlow)

Provides C++ API and interoperability with SYCL

Deep Learning Optimizations include:

- Asynchronous progress for compute communication overlap

- Dedication of cores to ensure optimal network use

- Optimizations for persistent collectives

- Collectives in low-precision data types

- Point to Point Operations

- Allgatherv

- Allreduce

- Alltoall/Alltoallv

- Broadcast

- Reduce

- ReduceScatter

#### **Point to Point**

Send/Recv

### Intel® MPI 2021.12 Update

- Intel<sup>®</sup> MPI is a portable message-passing library implementing the open MPI Standard: <u>https://www.intel.com/content/www/us/en/developer/tools/oneapi/mpi-library.htm</u>

- What's new:

- MPI-3 RMA GPU (host and device initiated)

- Including device-initiated kernel level load/store

- MPI 4.0 features

- Enhancements:

- GPU scalability optimizations

#

#### Performance

12<sup>th</sup> International Workshop on OpenCL and SYCL

## Intel® SHMEM: an OpenSHMEM Runtime with GPU-initiated Operations using SYCL

David Ozog, Md. Wasi-ur- Rahman, Lawrence Stewart

April 10, 2024

intel

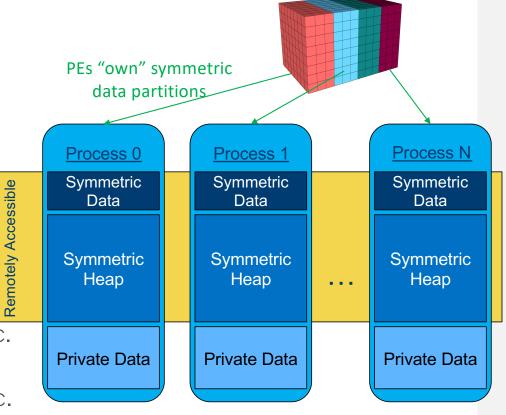

#### OpenSHMEM: Symmetric Memory

- Same size and layout at each process:

- Instances of symmetric objects present on every PE

- TYPE \*Y = shmem\_malloc(sizeof(TYPE))

- Put data to remote objects

- shmem\_put(&Y, &src\_data, nelems=1, pe=1)

- Remotely accessible memory is comprised of two segments

- Data segment (statically allocated)

- Heap segment (dynamically allocated)

#### APIs

| OpenSHMEM<br>standard<br>(ishmem.h) | <ul> <li>Library setup and query</li> <li>Memory management</li> <li>RMA, AMO, Signaling, Collective, Synchronization, Memory ordering (Host and Device)</li> <li>Host operations with symmetric memory objects resided in device memory</li> </ul> |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device<br>Extensions<br>(ishmemx.h) | <ul> <li>Work-group and sub-group level RMA, Signaling, Collectives, Synchronization, Memory ordering</li> <li>Host RMA operations using Level Zero</li> <li>Utility functions: print, timestamp</li> </ul>                                         |

| Not yet<br>released                 | <ul> <li>Threading Model</li> <li>Context (further clarifications needed) and Team management</li> <li>Non-blocking AMOs, vector-based wait-until / test</li> <li>Profiling interface</li> </ul>                                                    |

#### Intel® oneAPI Collective Communications Library Optimize Communication Patterns

- oneCCL provides optimized communication patterns for high performance on Intel CPUs & GPUs to distribute model training across multiple nodes

- Transparently supports many interconnects, such as Intel<sup>®</sup> Omni-Path Architecture, InfiniBand, & Ethernet

- Built on top of lower-level communication middleware-MPI & libfabrics

- Enables efficient implementations of collectives used for deep learning training: all-gather, all-reduce, and reduce-scatter, among others