# Towards performance portability of AI models using SYCL-DNN

Muhammad Tanvir – Staff Software Engineer – ML libraries

IWOCL-10-12 May 2022

## Outline

- Deep Learning Challenges

- Problem Statement performance portability

- How does SYCL help?

- Performance Evaluations

- Deep Learning on RISC-V

- Conclusions

# Deep Learning Challenges

- **Diversity** of Technologies and Techniques

- **Migrating** between Deep Learning frameworks

- Multiple implementations of same NN Optimization algorithms

- Maintainability of various version of low-level backend/libraries integrated in existing high-level frameworks

- Hardcoded implementation of inference engines for a restricted set of hardware

- Multiple implementations of same **NN algorithms** across various target **HW**

## Deep Learning Challenges

- Diversity of Technologies and Techniques.

- **Migrating** between DL framework.

- Multiple implementations of Same NN Optimization algorithms.

- Maintainability of various version of low-level libraries integrated in existing high-level frameworks.

- Hardcoded implementation of Inference engines for a restricted set of hardware.

- Multiple implementations of same NN algorithms across various target HW

#### Problem Statement

• Multiple implementations of same **NN algorithms** across various target **HW** – <u>is there a way around this</u>?

- An ideal solution(s) should:

- Be **portable** across different platforms

- Require little (to no) changes to the actual kernel code

- Yield acceptable performance as compared to vendor optimized code

- Have **backward compatibility (maintainability)**

## SYCL

#### • Supports cross-platform portability

• Different implementations of SYCL compilers provide a variety of targets

• Is maintainable

- Open-source implementations

- Kernel Code modifications?

- Performance Portability?

#### SYCL

- Kernel Code Modification?

- Possible Solution: Use C++ template meta programming to write highly parametrized kernels (<u>for the most compute</u> <u>intensive operations</u>)

#### • Benefits:

- Reuse the same kernel code

- Modify (tune) the template parameters to maximize performance on target hardware

# SYCL

• Performance Portability?

#### • Possible Solution:

- Tune the template parameters of the kernel to best match the underlying hardware\*

- Expose maximum performance out of the tuned kernel

- Acceptable Performance:

- Within 70%-80% range of vendor optimized code's performance

\*e.g. https://github.com/codeplaysoftware/sycl-blas/blob/master/tools/auto\_tuner/gen/intel\_gpu.json

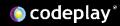

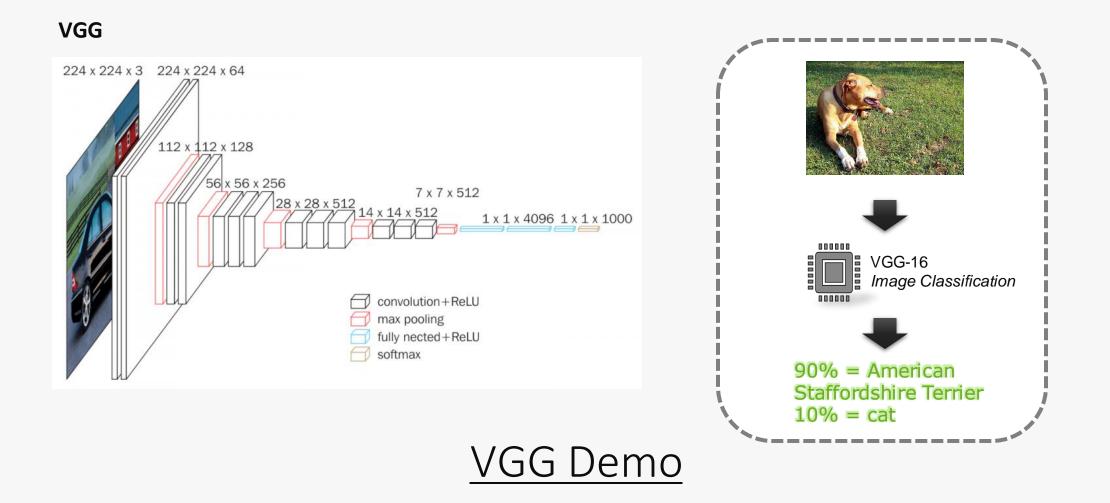

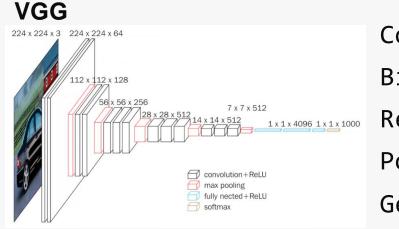

#### SYCL-DNN

- Conv

- Batchnorm

- Pool

- Softmax etc

https://github.com/codeplaysoftware/SYCL-DNN

#### • GEMM

- GEMV

- Reduction etc

https://github.com/codeplaysoftware/sycl-blas

- 1. Identify the most compute intensive operation(s)

- 2. Choose the target hardware

- 3. Tune SYCL code based on the target hardware

- 4. Evaluate performance

- 5. Repeat steps 2-4 for remaining target hardware

**()** codeplay<sup>®</sup>

1. Identify the most compute intensive operation

| Conv    | -> |

|---------|----|

| BiasAdd | -> |

| Relu    | -> |

|         |    |

Pooling ->

Gemm ->

Softmax ->

sycldnn::conv2d

sycldnn::biasAdd

sycldnn::relu

sycldnn::pooling

syclblas::gemm

sycldnn::softmax

std::string data\_dir{argv[1]}; auto input = read\_image\_data(argv[2], backend); Network network(input, output, data\_dir, backend, \*selector); network.add\_layer<ConvolutionLayer, 3>({3, 64, 224}); network.add\_layer<BiasAddLayer, 2>({64, 224}); network.add layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({64, 64, 224}); network.add\_layer<BiasAddLayer, 2>({64, 224}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({64, 224}); network.add\_layer<ConvolutionLayer, 3>({64, 128, 112}); network.add\_layer<BiasAddLayer, 2>({128, 112}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({128, 128, 112}); network.add\_layer<BiasAddLayer, 2>({128, 112}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({128, 112}); network.add\_layer<ConvolutionLayer, 3>({128, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({256, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({256, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({256, 56}); network.add\_layer<ConvolutionLayer, 3>({256, 512, 28}); network.add layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 28}); network.add\_layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 28}); network.add\_layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({512, 28}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({512, 14}); network.add\_layer<BiasAddLayer, 2>({4096, 1}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<FullyConnectedLayer, 1>({4096}); network.add\_layer<BiasAddLayer, 2>({4096, 1}); network.add layer<ReLULayer, 0>({}); network.add layer<FullyConnectedLayer, 1>({1000}); network.add\_layer<BiasAddLayer, 2>({1000, 1}); network.add\_layer<SoftmaxLayer, 0>({});

std::vector<float> output;

1. Identify the most compute intensive operation

#### **GEMM**

- Conv -> BiasAdd -> Relu -> Pooling -> Gemm ->

- Softmax ->

- sycldnn::conv2d

sycldnn::biasAdd

sycldnn::relu

sycldnn::pooling

syclblas::gemm

sycldnn::softmax

- std::string data\_dir{argv[1]}; auto input = read\_image\_data(argv[2], backend); Network network(input, output, data\_dir, backend, \*selector); network.add\_layer<ConvolutionLayer, 3>({3, 64, 224}); network.add\_layer<BiasAddLayer, 2>({64, 224}); network.add layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({64, 64, 224}); network.add\_layer<BiasAddLayer, 2>({64, 224}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({64, 224}); network.add\_layer<ConvolutionLayer, 3>({64, 128, 112}); network.add\_layer<BiasAddLayer, 2>({128, 112}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({128, 128, 112}); network.add\_layer<BiasAddLayer, 2>({128, 112}); network.add layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({128, 112}); network.add\_layer<ConvolutionLayer, 3>({128, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({256, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({256, 256, 56}); network.add\_layer<BiasAddLayer, 2>({256, 56}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({256, 56}); network.add\_layer<ConvolutionLayer, 3>({256, 512, 28}); network.add layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 28}); network.add\_layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 28}); network.add\_layer<BiasAddLayer, 2>({512, 28}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({512, 28}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<ConvolutionLayer, 3>({512, 512, 14}); network.add\_layer<BiasAddLayer, 2>({512, 14}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<PoolingLayer, 2>({512, 14}); network.add layer<FullyConnectedLayer, 1>({4096}); network.add\_layer<BiasAddLayer, 2>({4096, 1}); network.add\_layer<ReLULayer, 0>({}); network.add\_layer<FullyConnectedLayer, 1>({4096}); network.add\_layer<BiasAddLayer, 2>({4096, 1}); network.add layer<ReLULayer, 0>({}); network.add layer<FullyConnectedLayer, 1>({1000}); network.add\_layer<BiasAddLayer, 2>({1000, 1}); network.add\_layer<SoftmaxLayer, 0>({});

std::vector<float> output;

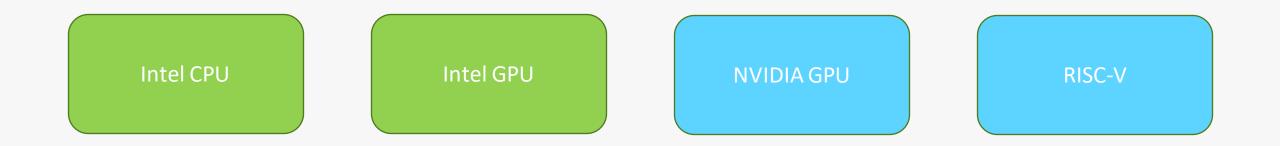

2. Choose the target hardware

- 3. Tune SYCL code based on the target hardware

- Target Hardware

- Intel(R) Core(TM) i7-6700K CPU @ 4 GHz

- Intel Corporation HD Graphics 530

- Most Compute Intensive Operation

- GEMM

- Tuning Methodology

- Lawson, John, and Mehdi Goli. "Performance portability through machine learning guided kernel selection in SYCL libraries." *Parallel Computing* 107 (2021): 102813.

# Tuning paradigm

- Every GEMM operation, in DNNs, has different compute intensity

- Most optimal solution

- One tuned kernel per GEMM operation

- Yields the best performance

- Size of the library increases drastically

- Semi-optimal solution

- One tuned kernel per DNN model

- Yields semi-optimal performance

- Limited no. of kernels in the library

350 160 140 300 120 250 100 200 80 150 60 100 40 50 20 0 0 SYCL-DNN SYCL-DNN + Tuning SYCL-DNN SYCL-DNN + Tuning oneDNN oneDNN ■ VGG16 Processing Time (ms) VGG16 Processing Time (ms)

Intel Corporation HD Graphics 530

\*With semi-optimal tuning regime

Intel(R) Core(TM) i7-6700K CPU

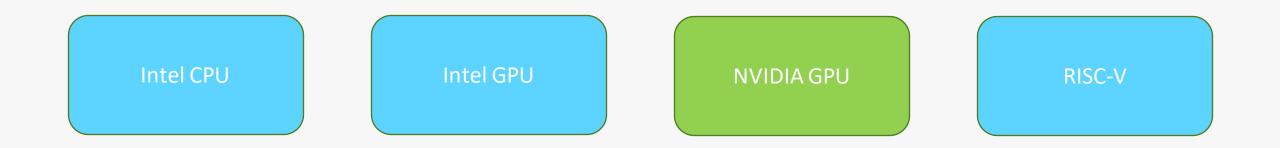

2. Choose the target hardware

3. Tune SYCL code based on the target hardware

- Target Hardware

- NVIDIA Titan RTX GPU 24 GB DDR6

- Most Compute Intensive Operation

- GEMM

- Tuning tool

- Modified version of SYCL-BLAS auto-tuner\*

\*https://github.com/codeplaysoftware/sycl-blas/tree/master/tools/auto\_tuner

3. Tune SYCL code based on the target hardware

- Search all possible GEMM configs\* exhaustively

- Choose a GEMM config

- Run the entire VGG16 (DNN) model and measure performance

- Record results for all possible GEMM configs

- Choose the GEMM config which yields the best performance

\*https://github.com/codeplaysoftware/sycl-blas/blob/master/tools/auto\_tuner/gen/nvidia\_gpu.json

2. Choose the target hardware

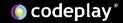

## Deep Learning on RISC-V

- Target Hardware

- RISC-V spike simulator single core

- Software Stack

- Acoran The Open Acceleration Platform\*

\*https://www.codeplay.com/solutions/acoran/

## Why Neural networks on RISC-V?

- Domain specific accelerators are required to achieve **cost-effective performance** on-chip

- Cost effective performance requires tuning the design to the needs of the workload required

- RISC-V ISA has a minimalist base integer instruction set and provides custom extensions

- An ideal starting point for creating special accelerators

- More companies are looking at RISC-V to enable AI software

- Designs can benefit from the RISC-V vector extension

- Enables vectorization for various application

- Helps achieve high compute density on chip

### Acoran – The Open Acceleration Platform

The Acoran platform provides all the supporting open-source libraries and frameworks needed to build this neural network demonstration

range<1> dimensions(matSize \* matSize); const property\_list props = {property::buffer::use\_host\_ptr()}; buffer<T> bA(MA, dimensions, props); buffer<T> bB(MB, dimensions, props); buffer<T> bC(MC, dimensions, props);

#### q.submit([&](handler& cgh) {

auto pA = bA.template get\_access<access::mode::read>(cgh); auto pB = bB.template get\_access<access::mode::read>(cgh); auto pC = bC.template get\_access<access::mode::write>(cgh); auto localRange = range<1>(blockSize \* blockSize);

cgh.parallel\_for<mxm\_kernel>(

// Current block

int blockX = it.get\_group(1); int blockY = it.get\_group(0);

// Current local item

int localX = it.get\_local\_id(1); int localY = it.get\_local\_id(0);

#### // Start in the A matri

int a\_start = matSize \* blockSize \* blockY;

// End in the b matrix

int a\_end = a\_start + matSize - 1;

// Start in the b matrix

int b\_start = blockSize \* blockX;

// Result for the current C(i,j) elemen

T tmp = 0.0f;

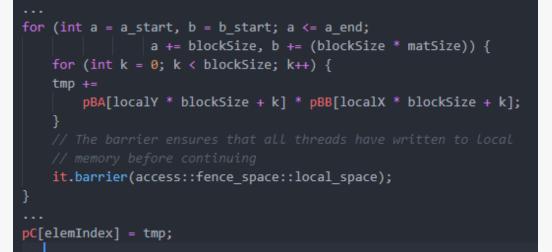

pB[b + matSize \* localY + localX]; it.barrier(access::fence\_space::local\_space); // Now each thread adds the value of its sum for (int k = 0; k < blockSize; k++) {</pre>

tmp +=

pBA[localY \* blockSize + k] \* pBB[localX \* blockSize -

// The barrier ensures that all threads have written to local

// memory before continuing

it.barrier(access::fence\_space::local\_space);

pC[elemIndex] = tmp;

}

#### **GEMM** Operator

#### Main Computation

range<1> dimensions(matSize \* matSize); const property\_list props = {property::buffer::use\_host\_ptr()}; buffer<T> bA(MA, dimensions, props); buffer<T> bB(MB, dimensions, props); buffer<T> bC(MC, dimensions, props);

#### q.submit([&](handler& cgh) {

auto pA = bA.template get\_access<access::mode::read>(cgh); auto pB = bB.template get\_access<access::mode::read>(cgh); auto pC = bC.template get\_access<access::mode::write>(cgh); auto localRange = range<1>(blockSize \* blockSize);

range<2>(blockSize, blockSize)},

[=](nd\_item<2> it) {

// Current block

int blockX = it.get\_group(1); int blockY = it.get\_group(0);

// Current Local item

int localX = it.get\_local\_id(1);

int localY = it.get\_local\_id(0);

// Start in the A matrix

int a\_start = matSize \* blockSize \* blockY; // End in the b matrix int a\_end = a\_start + matSize - 1; // Start in the b matrix int b\_start = blockSize \* blockX;

it.barrier(access::fence\_space::local\_space);

####

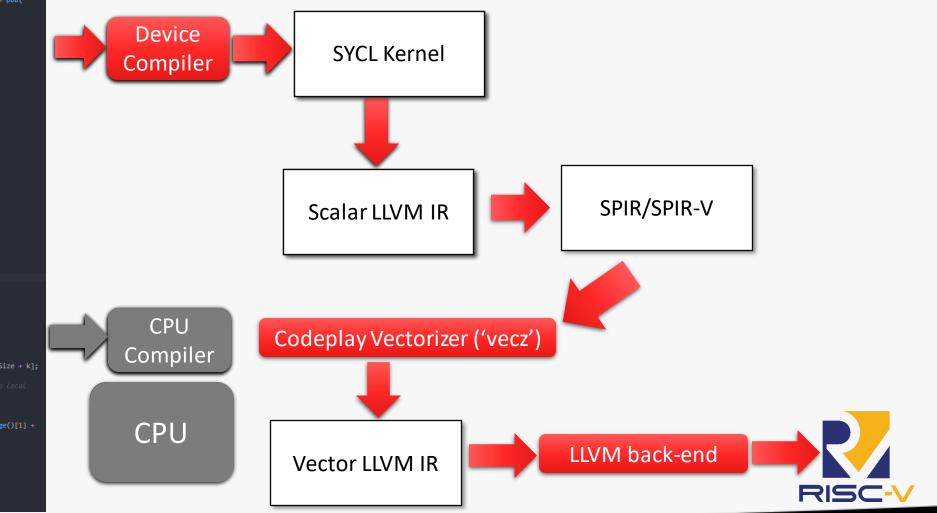

RISC-V/RVV Kernel compilation flow FC

return false:

#### Deep Learning on RISC-V

#### Conclusions

- SYCL-DNN / SYCL-BLAS have support for efficient acceleration of popular DNNs

- Acoran platform provides an end-to-end compute stack for accelerating DNNs on RISC-V

- https://developer.codeplay.com/products/acoran/pre-alpha

- Recent Update: Adding SYCL to upstream ONNX Runtime

- https://github.com/codeplaysoftware/onnxruntime

# Thank you

#### muhammad.tanvir@codeplay.com

We're Hiringet Coleparton/careers

www

@codeplaysoft inf

info@codeplay.com

codeplay.com